# Compiler-Assisted Energy Optimization for Clustered VLIW Processors

A Thesis

Submitted for the Degree of

**Doctor of Philosophy**

in the Faculty of Engineering

by

**Rahul Nagpal**

Department of Computer Science and Automation

**Indian Institute of Science**

Bangalore – 560 012, India

March 2008

सर्वं मंगलं मांगल्ये शिवे सर्वार्थं साधिके ।

शरण्ये अपन्यके गौरि नारायणि नमोऽस्तु ते ॥

# Abstract

Clustered architecture processors are preferred for embedded systems because centralized register file architectures scale poorly in terms of clock rate, chip area, and power consumption. Although clustering helps by improving clock speed, reducing energy consumption of the logic, and making the design simpler, it introduces extra overheads by way of inter-cluster communication. This communication happens over long wires having high load capacitance which leads to delay in execution and significantly high energy consumption. Inter-cluster communication also introduces many short idle cycles, thereby significantly increasing the overall leakage energy consumption in the functional units. The trend towards miniaturization of devices (and associated reduction in threshold voltage) makes energy consumption in interconnects and functional units even worse and limits the usability of clustered architectures in smaller technologies.

In the past, study of leakage energy management at the architectural level has mostly focused on storage structures such as cache. Relatively, little work has been done on architecture level leakage energy management in functional units in the context of superscalar processors and energy efficient scheduling in the context of VLIW architectures. In the absence of any high level model for interconnect energy estimation, the primary focus of research in the context of interconnects has been to reduce the latency of communication and evaluation of various inter-cluster communication models. To the best of our knowledge, there has been no such work in the past from the point of view of energy efficiency targeting clustered VLIW architectures specifically focusing on smaller technologies.

Technological advancements now permit design of interconnects and functional units

with varying performance and power modes. In this thesis, we propose scheduling algorithms that aggregate the scheduling slack of instructions and communication slack of data values to exploit the low power modes of interconnects and functional units. We also propose a high level model for estimation of interconnect delay and energy (in contrast to low-level circuit level model proposed earlier) that makes it possible to carry out architectural and compiler optimizations specifically targeting the interconnect. Finally, we present synergistic combination of these algorithms that simultaneously saves energy in functional units and interconnects to improve the usability of clustered architectures by achieving better overall energy-performance trade-offs.

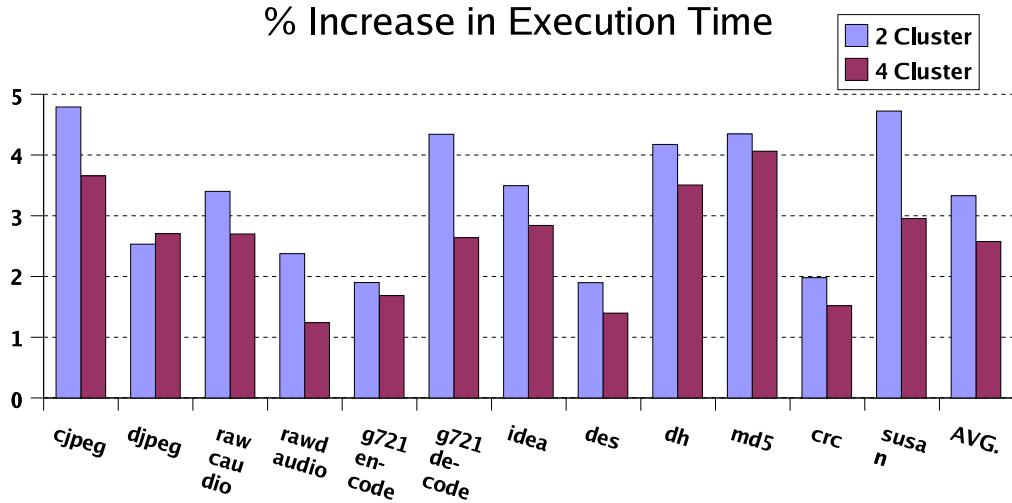

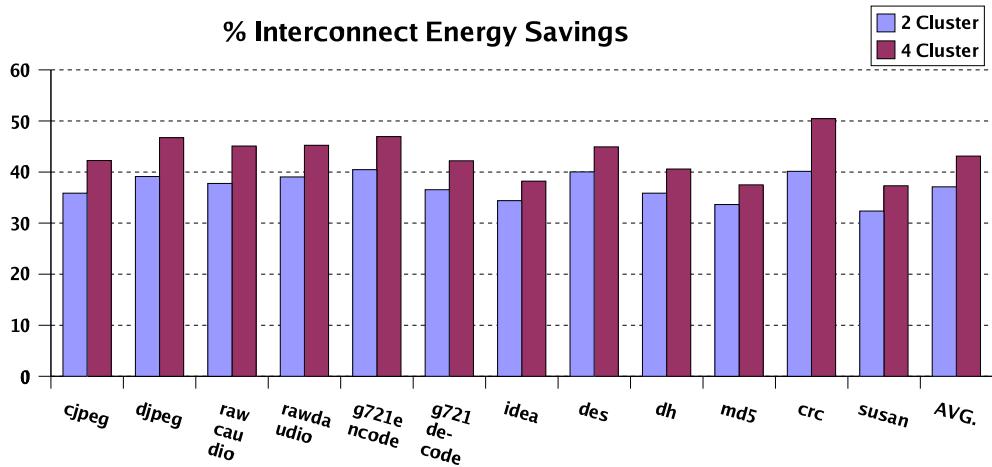

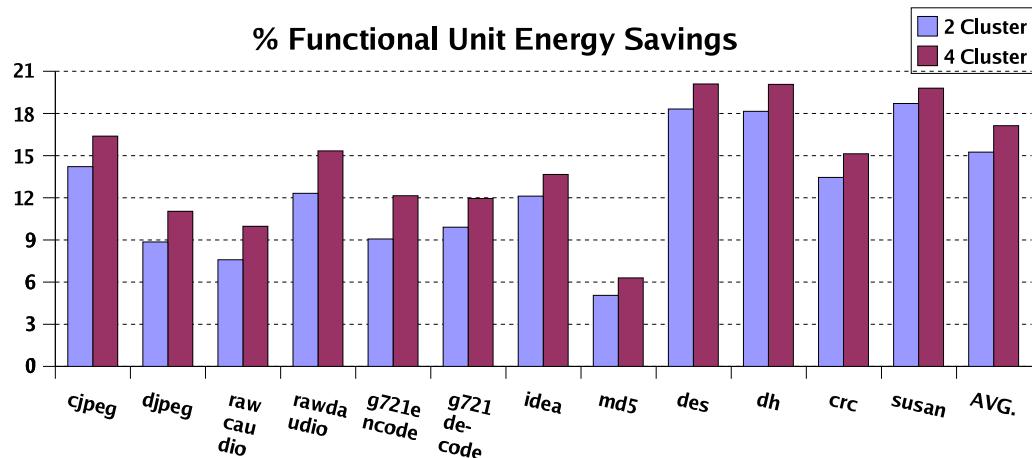

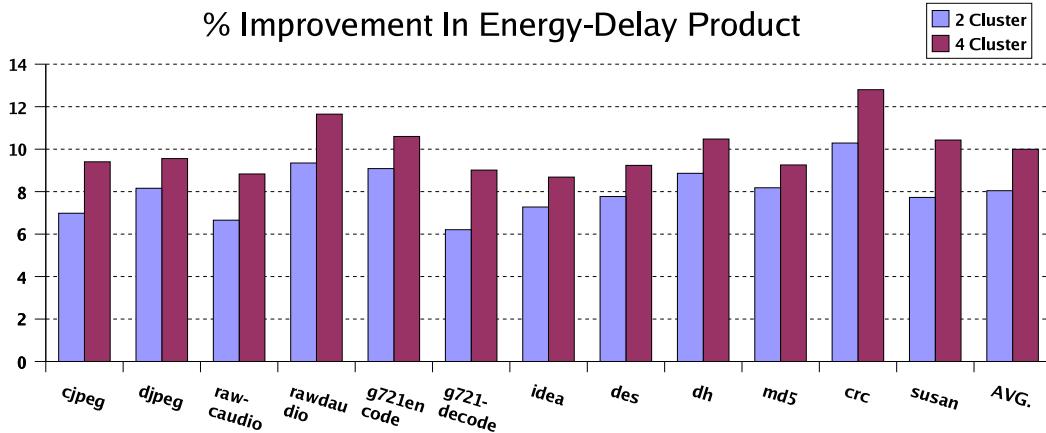

Our compiler assisted leakage energy management scheme for functional units reduces the energy consumption of functional units approximately by 15% and 17% in the context of a 2-clustered and a 4-clustered VLIW architecture respectively with negligible performance degradation over and above that offered by a hardware-only scheme. The interconnect energy optimization scheme improves the energy consumption of interconnects on an average by 41% and 46% for a 2-clustered and a 4-clustered machine respectively with 2% and 1.5% performance degradation. The combined scheme obtains slightly better energy benefit in functional units and 37% and 43% energy benefit in interconnect with slightly higher performance degradation. Even with the conservative estimates of contribution of functional unit and interconnect to overall processor energy consumption, the proposed combined scheme obtains on an average 8% and 10% improvement in overall energy-delay product with 3.5% and 2% performance degradation for a 2-clustered and a 4-clustered machine respectively. We present a detailed experimental evaluation of the proposed schemes using the Trimaran compiler infrastructure.

# Acknowledgments

I would like to express my deep gratitude to my research supervisor, Prof. Y. N. Srikant, for providing me an opportunity to work under his supervision. Prof. Y. N. Srikant is an excellent adviser who is always willing to listen, encourage, and give insightful comments and valuable criticism. This dissertation would have been a dream for me without his support, inspiration, and constant encouragement.

I would like to thank Prof. Amrutur Bhardwaj for many important technical discussions especially towards end of my thesis. I am also thankful to the faculty of the Department of Computer Science and Automation, Prof. Priti Shankar, Prof. Narahari, Prof. Narasimha Murthy, and Prof. Mathew Jacob in particular, for clarifying doubts, refining ideas, and for the constant encouragement.

Particular thanks go to the Philips Research for funding the part of this research work. Thanks also to Microsoft Research Labs, Redmond, USA for providing me an exciting period of 3 months of internship which helped me to understand the industry style of research.

My heartfelt thanks to my dear lab mates at compiler lab who have provided wonderful company and stimulating environment; without them this process would have been much difficult. In particular, I would like to thank Arun and Anand Vardhan. Many thanks to the lab staff of the Compiler Laboratory, Pushpraj in particular, for their support and assistance. I would also like to thank my other friends in IISc for a constant source of mild distraction that prevented me from burning out during the course of my research.

I can not thank my parents enough for their countless sacrifices. They have constantly talked me out of worries and it is due to their support and encouragement that I could face most difficult times and still could come this far.

Finally, Thanks to all who supported me directly or indirectly in this period of my life.

# Publications Based on the Thesis

## Conferences

1. Rahul Nagpal and Y. N. Srikant. Compiler-assisted Leakage Energy Optimization for Clustered VLIW Architectures, Proceedings of the International Conference on Embedded Software (EMSOFT'06), Seoul, Korea, October 2006.

2. Rahul Nagpal and Y. N. Srikant. Exploring Energy-Performance Trade-offs for Heterogeneous Interconnect Clustered VLIW Processors, Proceedings of the International Conference on High Performance Computing (HiPC'06), Bangalore, India, December 2006.

3. Rahul Nagpal, Arvind Madan, Amrutur Bharadwaj, and Y. N. Srikant. INTACTE: An Interconnect Area, Delay, and Energy Estimation Tool for Micro-architectural Explorations, Proceedings of the International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CASES'07), Salzburg, Austria, October 2007.

4. Rahul Nagpal and Y. N. Srikant. Register File Energy Optimization for Clustered VLIW Architectures, Proceedings of the International Symposium on Computer Architecture and High Performance Computing (SBAC-PAD'07), Gramado, RS, Brazil October 2007.

5. Rahul Nagpal and Y. N. Srikant. Compiler-assisted Instruction Decoder Energy Optimization for Clustered VLIW Architectures, Proceedings of the International Conference on High Performance Computing (HiPC'07), Goa, India, December 2007.

## **Poster Presentations**

1. Rahul Nagpal. Energy Efficient Cross-path Scheduling for Clustered VLIW Processors, Poster Presentation at International Conference on Language, Compilers, and Tool Support for Embedded Systems (LCTES'06), Ottawa, Canada, June 2006.

2. Rahul Nagpal and Y. N. Srikant. Energy Optimization for Clustered VLIW Architectures, Poster Presentation at Third International Summer School on Advanced Computer Architecture and Compilation for Embedded Systems (ACACES'07), L'Aquila, Italy, July 2007.

## **Journals**

1. Rahul Nagpal and Y. N. Srikant. Compiler-Assisted Energy Optimization for Clustered VLIW Architectures (under Review)

2. Rahul Nagpal and Y. N. Srikant. Compiler-Assisted Power Optimization for Hot Spots in Clustered VLIW Architectures (under Review)

3. Rahul Nagpal, Arvind Madan, Amrutur Bharadwaj, and Y. N. Srikant. An Interconnect Area, Delay, and Energy Estimation Methodology and its application for Micro-architectural Explorations (under Preparation)

# Contents

|                                                               |    |

|---------------------------------------------------------------|----|

| <b>Abstract</b>                                               | ii |

| <b>Acknowledgments</b>                                        | iv |

| <b>Publications Based on the Thesis</b>                       | v  |

| <b>1 Introduction</b>                                         | 1  |

| 1.1 The State-of-art . . . . .                                | 5  |

| 1.2 Our Approach . . . . .                                    | 6  |

| 1.3 Outline of the Thesis . . . . .                           | 9  |

| <b>2 Related Work</b>                                         | 10 |

| 2.1 Power Basics and Metrics . . . . .                        | 10 |

| 2.2 Circuit and Logic Level Techniques . . . . .              | 12 |

| 2.2.1 Dynamic Energy Optimization in Logic . . . . .          | 12 |

| 2.2.2 Leakage Energy Optimization in Logic . . . . .          | 13 |

| 2.2.3 Interconnect Energy Optimization . . . . .              | 14 |

| 2.3 Architectural Techniques for Power Optimization . . . . . | 14 |

| 2.3.1 Dynamic Voltage Scaling . . . . .                       | 15 |

| 2.3.2 Leakage Energy Management of Other Devices . . . . .    | 17 |

| 2.4 Software Level Power management . . . . .                 | 18 |

| 2.4.1 Compiler-Directed Power Management . . . . .            | 18 |

| 2.4.2 Application and OS Level Power Management . . . . .     | 19 |

| 2.5 Hardware/Software Co-Optimization . . . . .               | 20 |

| 2.6 Power Management in Commercial Processor . . . . .        | 21 |

|          |                                                             |           |

|----------|-------------------------------------------------------------|-----------|

| 2.7      | Energy Estimation and Energy Modeling . . . . .             | 23        |

| 2.8      | Limitations of the Earlier Work . . . . .                   | 24        |

| <b>3</b> | <b>Clustered VLIW Architectures and Experimental Setup</b>  | <b>26</b> |

| 3.1      | Clustered Architectures . . . . .                           | 26        |

| 3.1.1    | Clustering Overheads . . . . .                              | 30        |

| 3.2      | Some Clustered Architectures . . . . .                      | 31        |

| 3.2.1    | VelociTI Architecture . . . . .                             | 31        |

| 3.2.2    | Lx Architecture . . . . .                                   | 34        |

| 3.2.3    | Other Clustered Architectures . . . . .                     | 35        |

| 3.3      | Cluster Scheduling . . . . .                                | 36        |

| 3.3.1    | Preprocessing . . . . .                                     | 37        |

| 3.3.2    | Instruction Selection . . . . .                             | 37        |

| 3.3.3    | Cluster Assignment . . . . .                                | 38        |

| 3.3.4    | Functional Unit Assignment . . . . .                        | 39        |

| 3.3.5    | Cross-path Assignment . . . . .                             | 39        |

| 3.4      | Trimaran Framework . . . . .                                | 40        |

| 3.5      | Experimental Setup . . . . .                                | 41        |

| <b>4</b> | <b>Leakage Energy Management for Functional Units</b>       | <b>44</b> |

| 4.1      | Introduction . . . . .                                      | 44        |

| 4.2      | Motivation . . . . .                                        | 46        |

| 4.3      | The Scheduling Algorithm . . . . .                          | 51        |

| 4.3.1    | Prioritizing the Ready Instructions . . . . .               | 51        |

| 4.3.2    | Cluster Assignment . . . . .                                | 52        |

| 4.3.3    | Functional Unit Binding . . . . .                           | 53        |

| 4.3.4    | An Example . . . . .                                        | 54        |

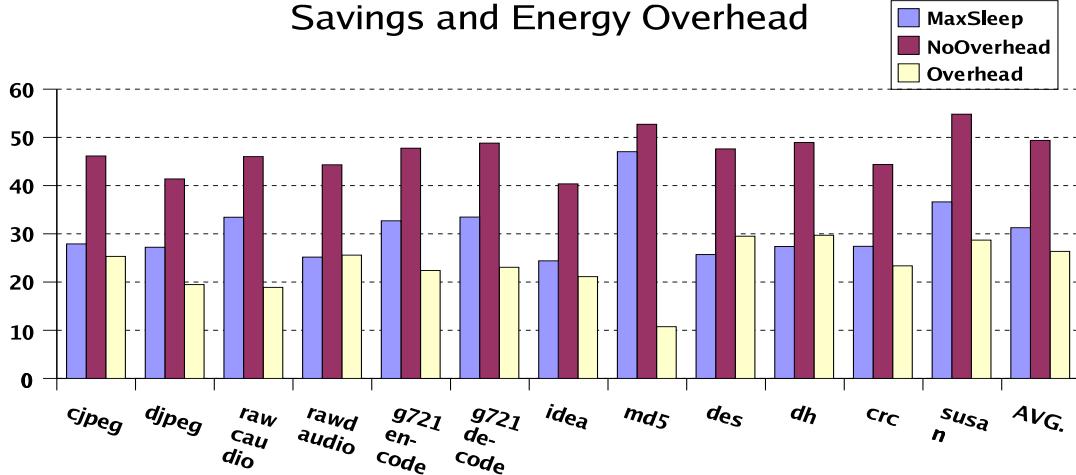

| 4.4      | Experimental Evaluation . . . . .                           | 57        |

| 4.4.1    | Energy Model . . . . .                                      | 57        |

| 4.4.2    | Results . . . . .                                           | 59        |

| 4.4.3    | Sensitivity Analysis . . . . .                              | 62        |

| 4.5      | Application in the Context of Instruction Decoder . . . . . | 63        |

|          |                                                                          |           |

|----------|--------------------------------------------------------------------------|-----------|

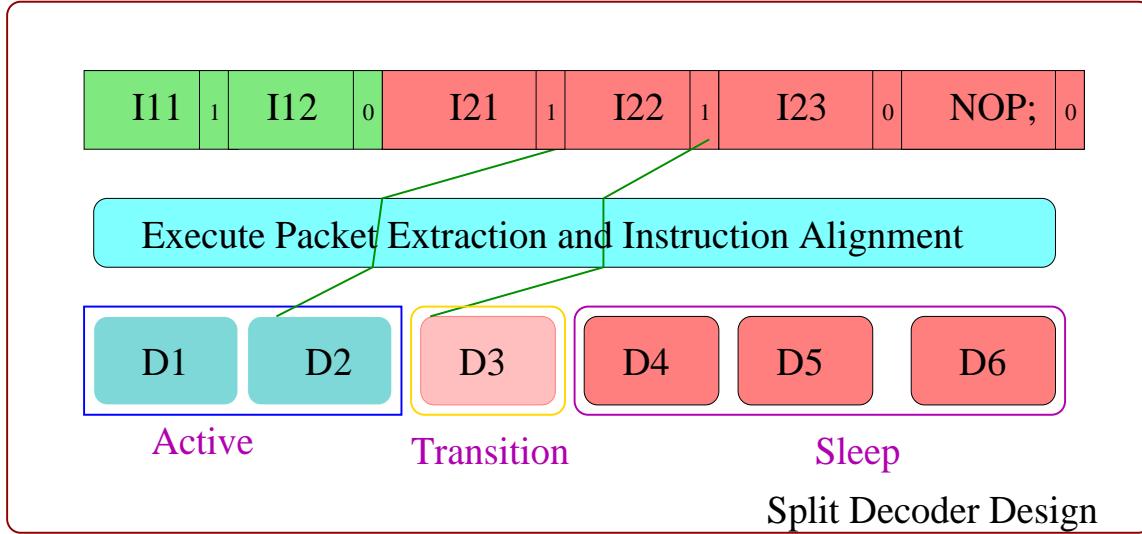

| 4.5.1    | Split Decoder Design . . . . .                                           | 64        |

| 4.5.2    | Experimental Evaluation . . . . .                                        | 66        |

| 4.6      | Related Work . . . . .                                                   | 68        |

| 4.6.1    | Scheduling for Clustered Architectures . . . . .                         | 68        |

| 4.6.2    | Architectural Approaches for Leakage Energy Management . . . . .         | 70        |

| 4.6.3    | Energy-Efficient Scheduling . . . . .                                    | 72        |

| 4.7      | Conclusions . . . . .                                                    | 73        |

| <b>5</b> | <b>INTACTE: An Interconnect Area, Delay, and Energy Estimation Model</b> | <b>74</b> |

| 5.1      | Introduction . . . . .                                                   | 74        |

| 5.2      | INTACTE Tool Description . . . . .                                       | 77        |

| 5.3      | Modeling The Interconnect . . . . .                                      | 80        |

| 5.3.1    | Delay Characterization . . . . .                                         | 82        |

| 5.3.2    | Power Characterization . . . . .                                         | 83        |

| 5.4      | Experimental Results . . . . .                                           | 85        |

| 5.5      | Related Work . . . . .                                                   | 90        |

| 5.6      | Conclusions . . . . .                                                    | 91        |

| <b>6</b> | <b>Energy Optimization for Interconnects</b>                             | <b>93</b> |

| 6.1      | Introduction . . . . .                                                   | 93        |

| 6.2      | Motivation . . . . .                                                     | 94        |

| 6.3      | The Scheduling Algorithm . . . . .                                       | 97        |

| 6.3.1    | Prioritizing the Ready Instructions . . . . .                            | 97        |

| 6.3.2    | Cluster Assignment . . . . .                                             | 99        |

| 6.3.3    | Cross-path Binding . . . . .                                             | 99        |

| 6.3.4    | An Example . . . . .                                                     | 101       |

| 6.4      | Experimental Evaluation . . . . .                                        | 102       |

| 6.4.1    | Energy Model . . . . .                                                   | 103       |

| 6.4.2    | Results . . . . .                                                        | 103       |

| 6.4.3    | Sensitivity Analysis . . . . .                                           | 105       |

| 6.5      | Related Work . . . . .                                                   | 106       |

| 6.6      | Conclusions . . . . .                                                    | 107       |

|                                                                                |            |

|--------------------------------------------------------------------------------|------------|

| <b>7 Integrated Energy Optimization for Functional Units and Interconnects</b> | <b>108</b> |

| 7.1 Introduction . . . . .                                                     | 108        |

| 7.2 The Scheduling Algorithm . . . . .                                         | 108        |

| 7.2.1 Prioritizing the Ready Instructions . . . . .                            | 109        |

| 7.2.2 Cluster Assignment . . . . .                                             | 110        |

| 7.2.3 Functional Unit Binding . . . . .                                        | 110        |

| 7.2.4 Cross-path Binding . . . . .                                             | 111        |

| 7.3 Scheduler Implementation . . . . .                                         | 111        |

| 7.4 Experimental Evaluation . . . . .                                          | 116        |

| 7.4.1 Results . . . . .                                                        | 117        |

| 7.5 Conclusions . . . . .                                                      | 120        |

| <b>8 Conclusions and Future Directions</b>                                     | <b>121</b> |

| 8.1 Conclusions . . . . .                                                      | 121        |

| 8.2 Future Directions . . . . .                                                | 124        |

| <b>Bibliography</b>                                                            | <b>126</b> |

# List of Figures

|      |                                                                                                 |    |

|------|-------------------------------------------------------------------------------------------------|----|

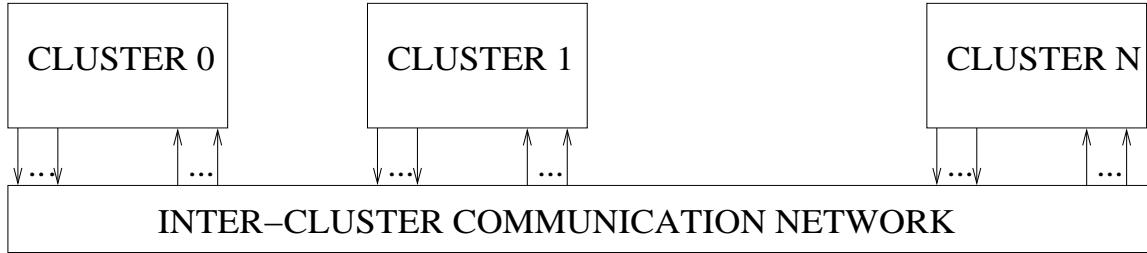

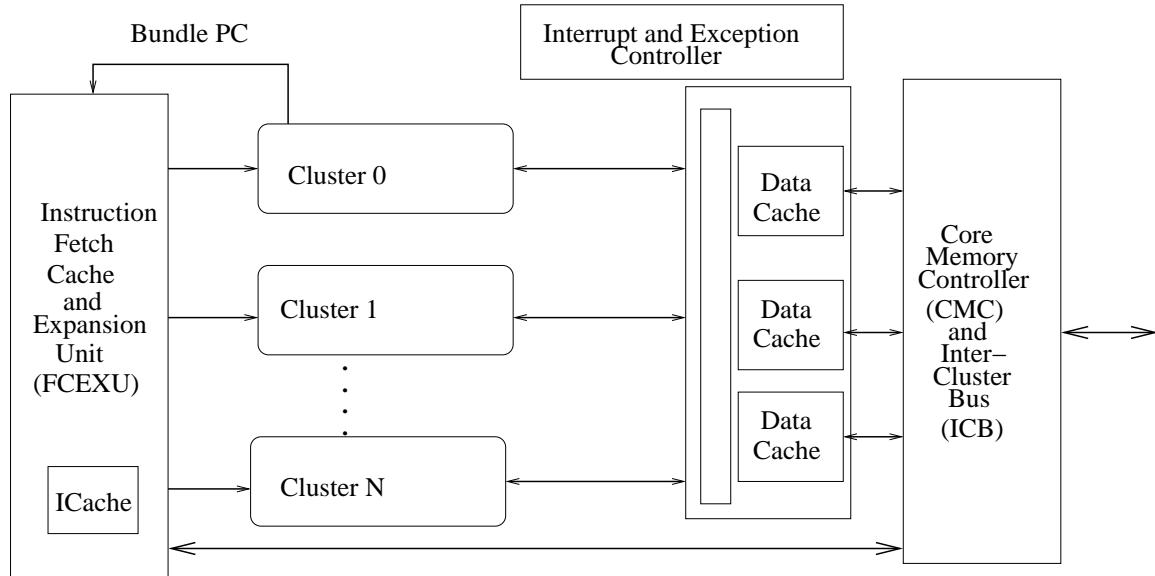

| 3.1  | A General Clustered VLIW Architecture . . . . .                                                 | 29 |

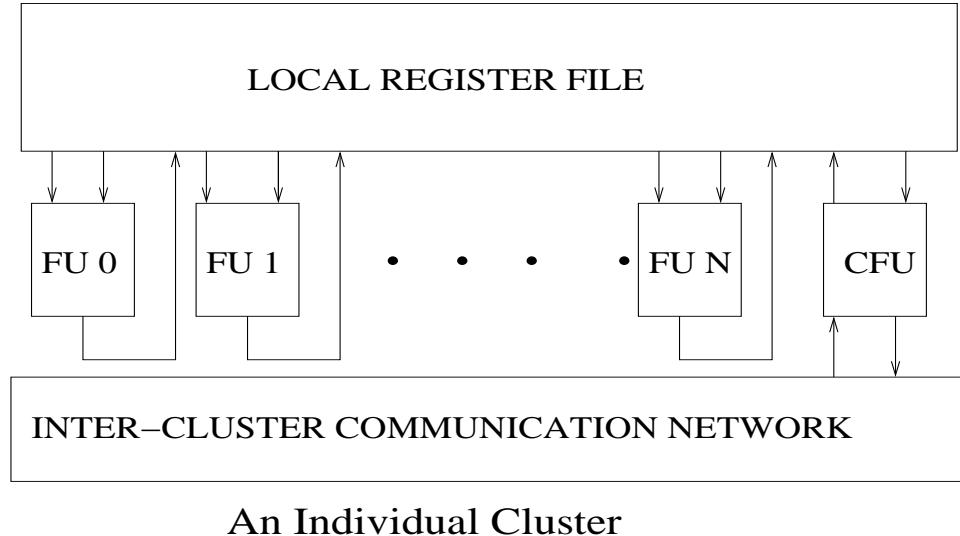

| 3.2  | A Cluster . . . . .                                                                             | 30 |

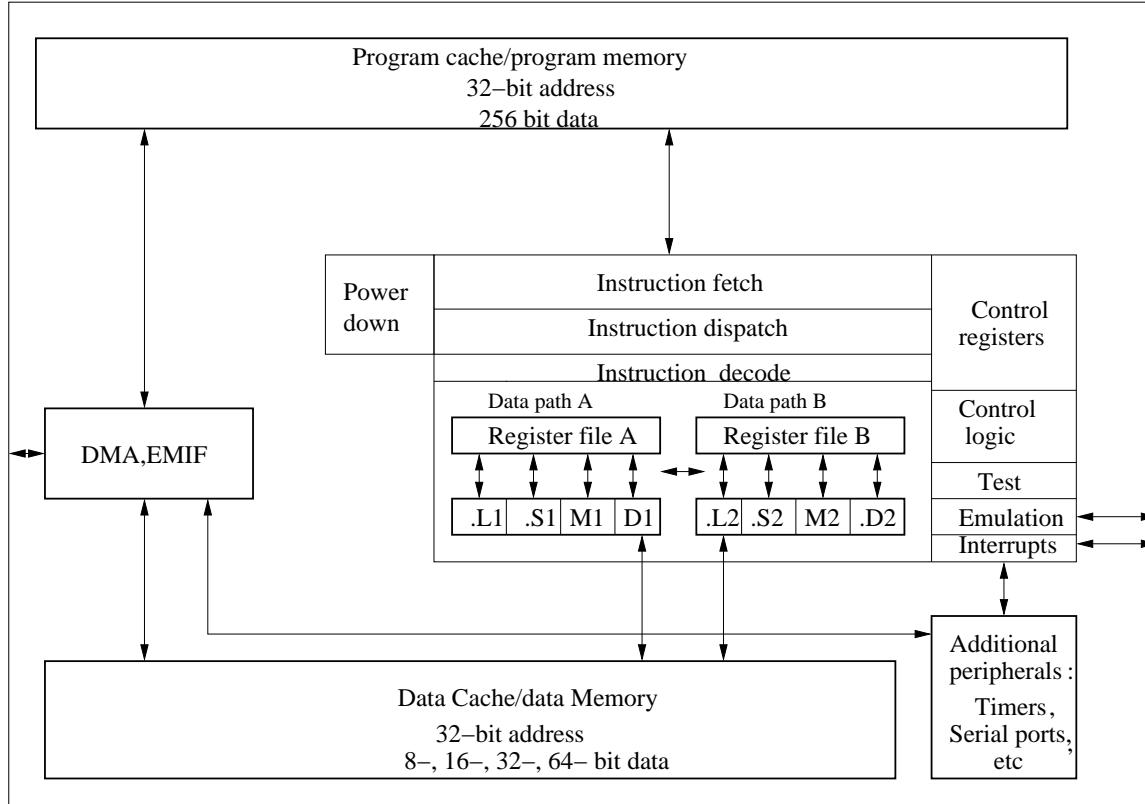

| 3.3  | VelociTI Architecture Block Diagram . . . . .                                                   | 32 |

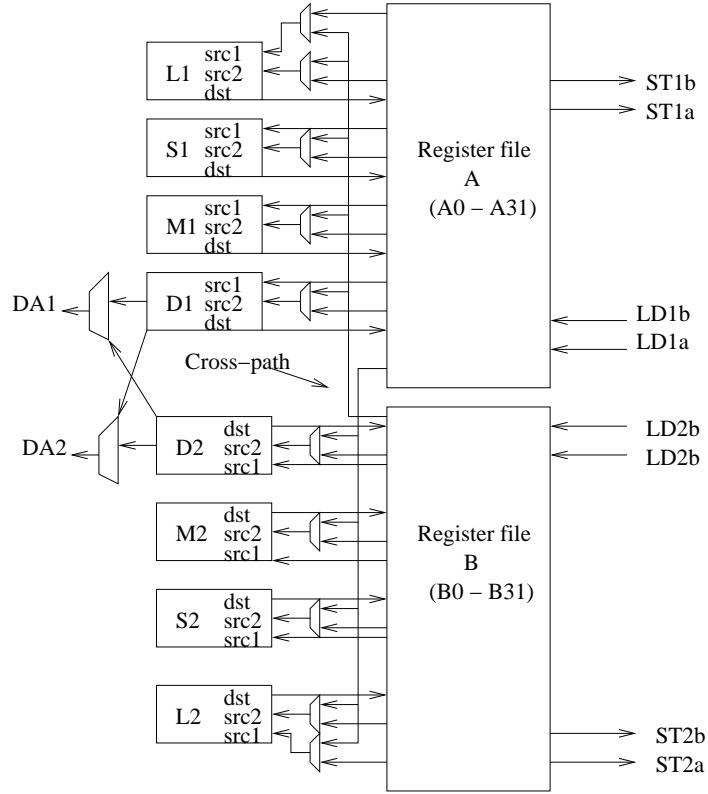

| 3.4  | TMS320C64X CPU Data Paths . . . . .                                                             | 33 |

| 3.5  | Lx Architecture Block Diagram . . . . .                                                         | 34 |

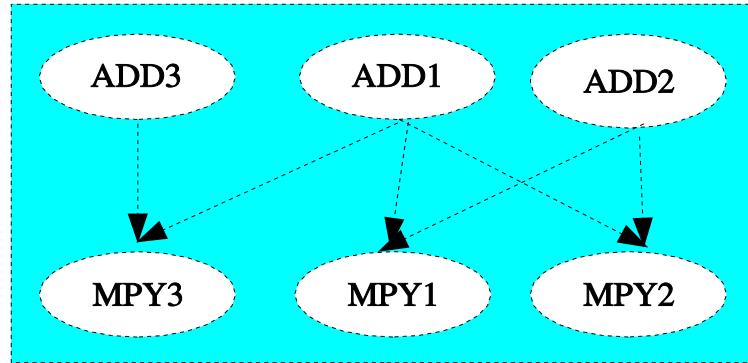

| 3.6  | Communications Required as a Result of a Cluster Assignment . . . . .                           | 39 |

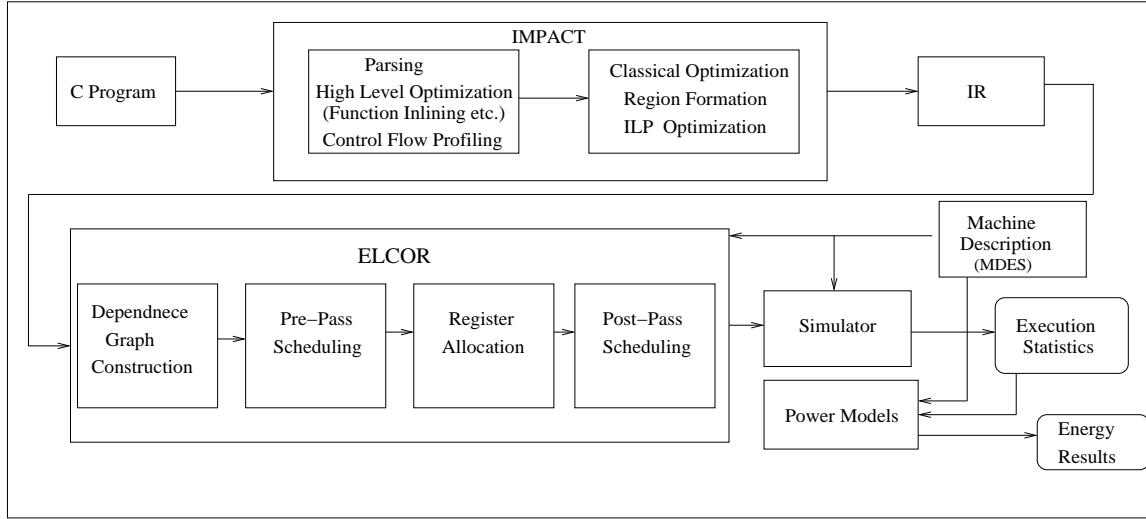

| 3.7  | Implementation Framework on Trimaran Infrastructure . . . . .                                   | 41 |

| 4.1  | % Savings for 'MaxSleep' and 'NoOverhead' Policies . . . . .                                    | 47 |

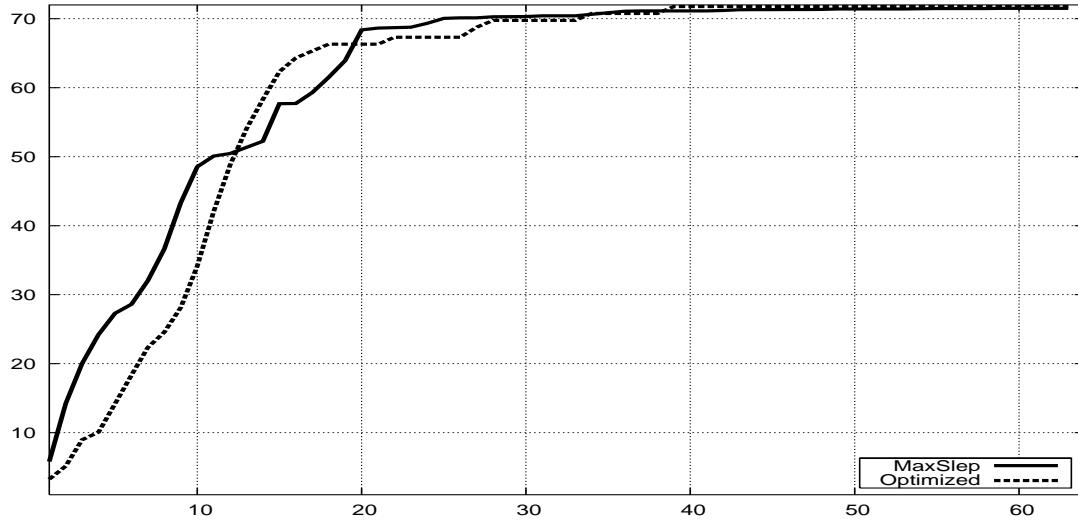

| 4.2  | % Cumulative Distribution of Idle Cycles . . . . .                                              | 48 |

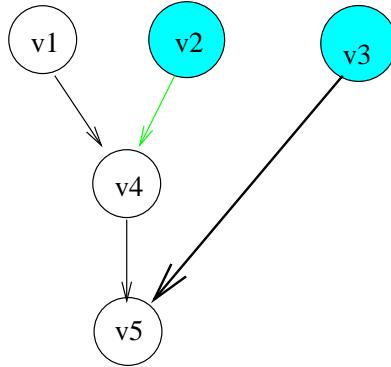

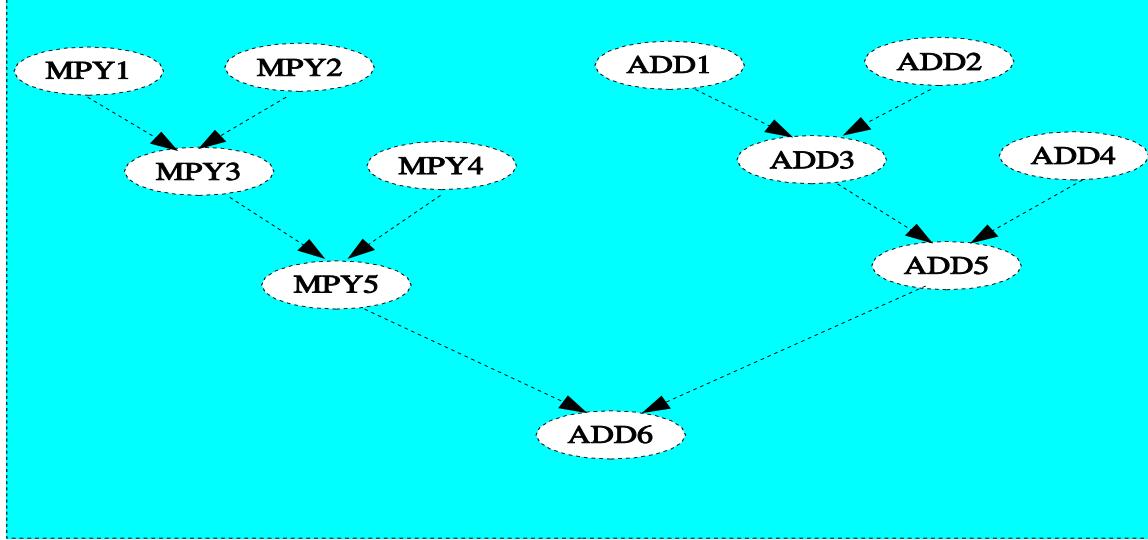

| 4.3  | An Example Data Dependency Graph . . . . .                                                      | 54 |

| 4.4  | Schedules for VLIW Architecture (a) Schedule 1 (b) Schedule 2 . . . . .                         | 55 |

| 4.5  | Schedules for Clustered VLIW Architecture (a) Schedule 3 (b) Schedule 4 . . . . .               | 55 |

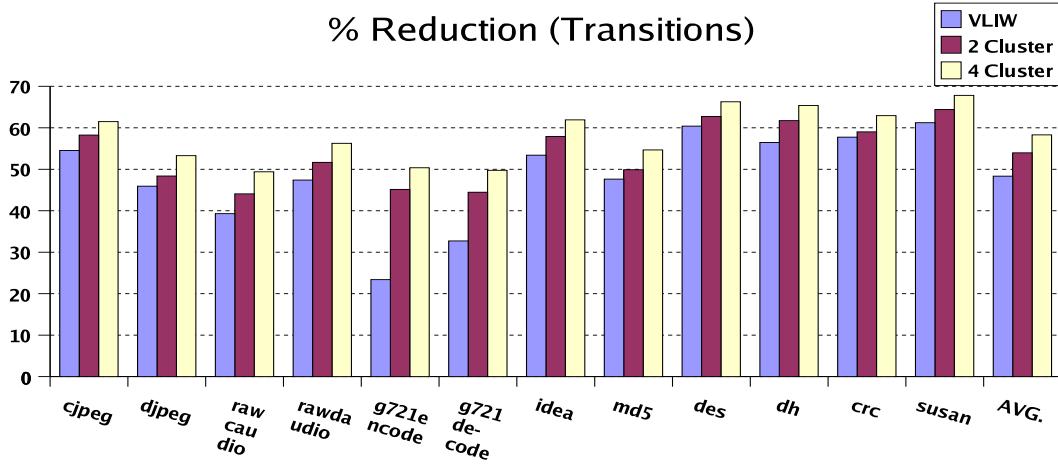

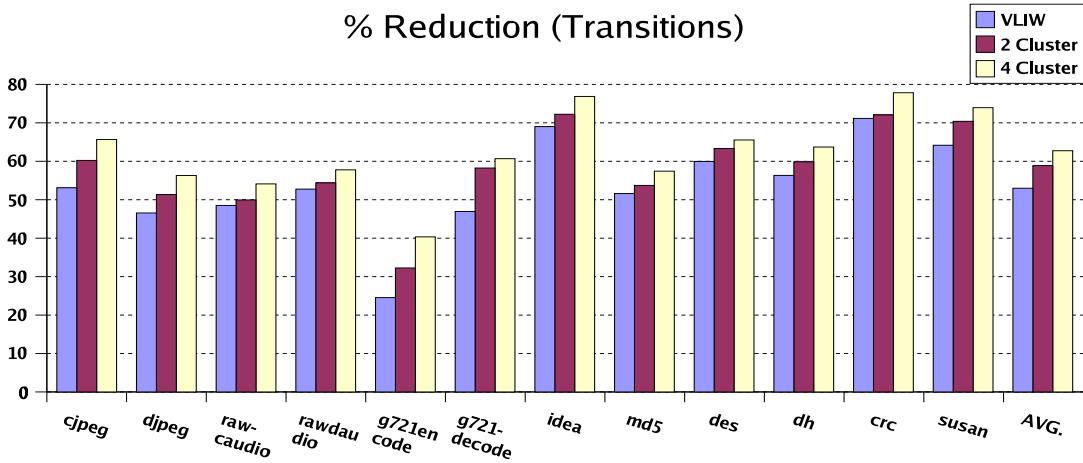

| 4.6  | % Reduction in Transitions with Scheduling w.r.t. Hardware Only Scheme . . . . .                | 59 |

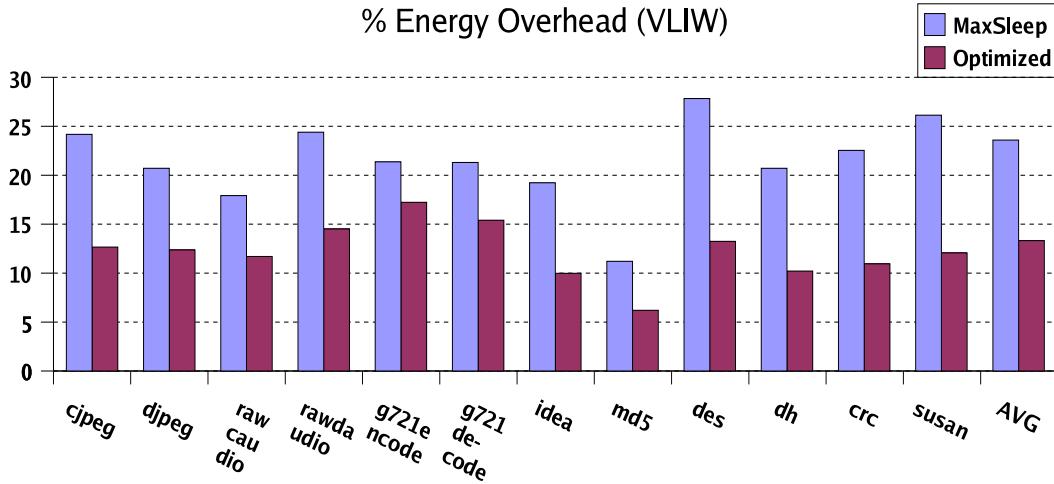

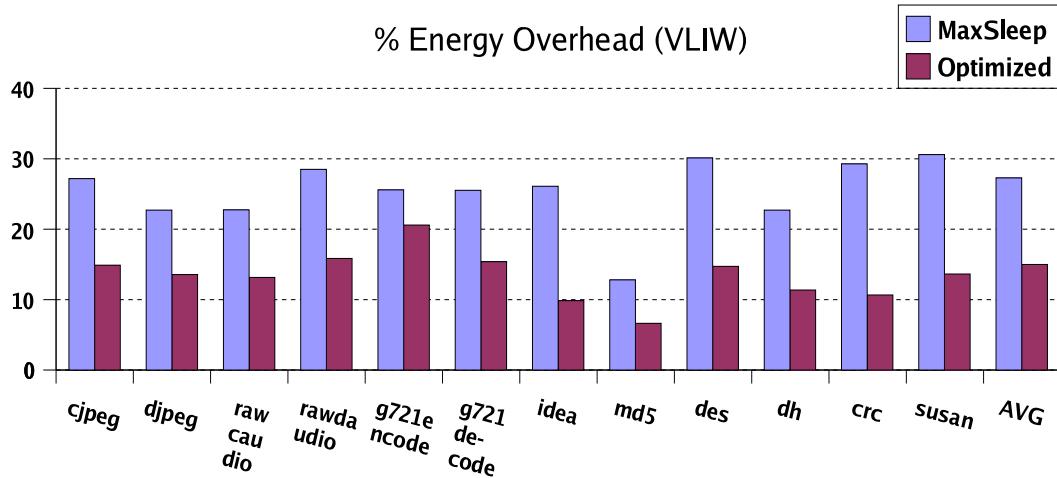

| 4.7  | % Increase in Functionl Unit Energy w.r.t Hypothetical No-overhead Scheme (VLIW) . . . . .      | 60 |

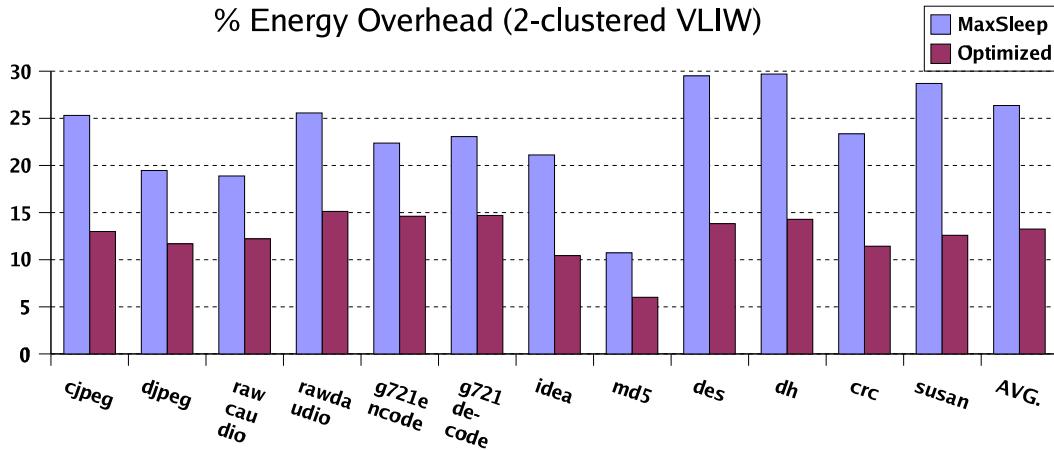

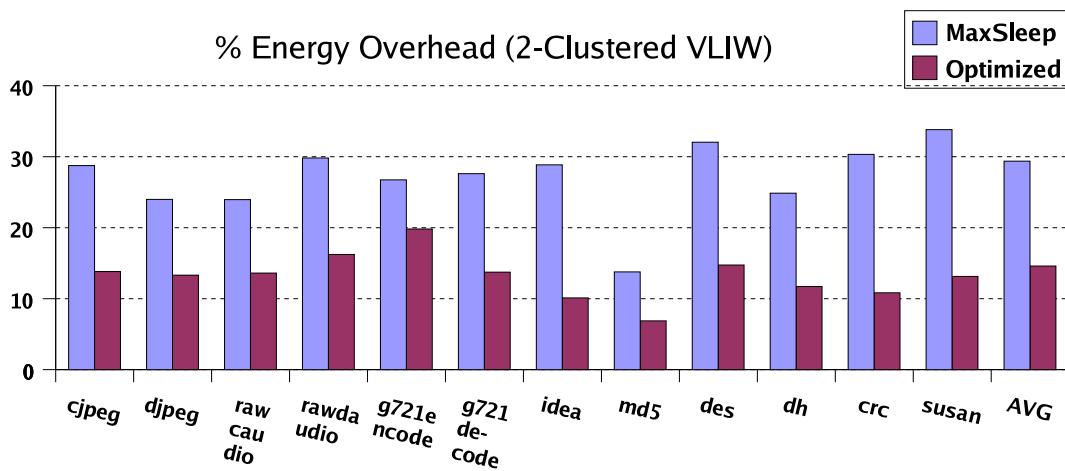

| 4.8  | % Increase in Functionl Unit Energy w.r.t Hypothetical No-overhead Scheme (2 Cluster) . . . . . | 61 |

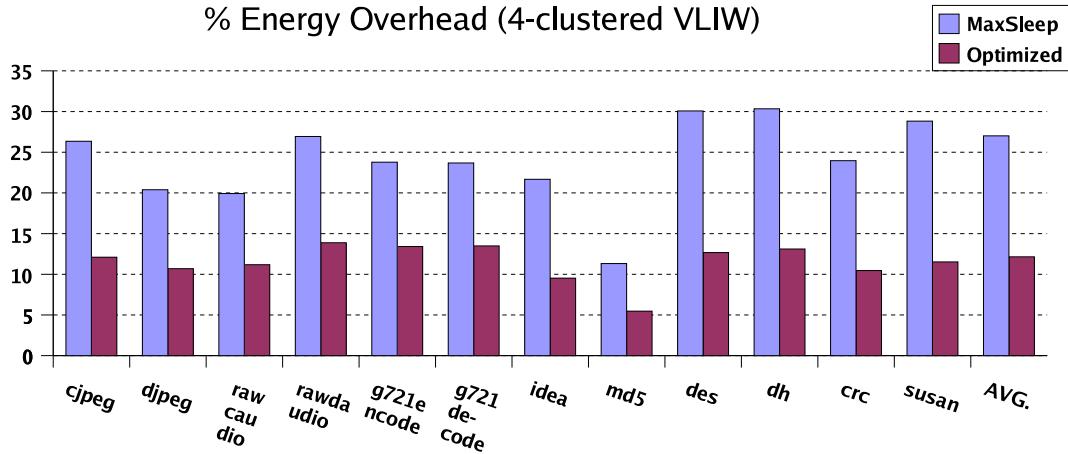

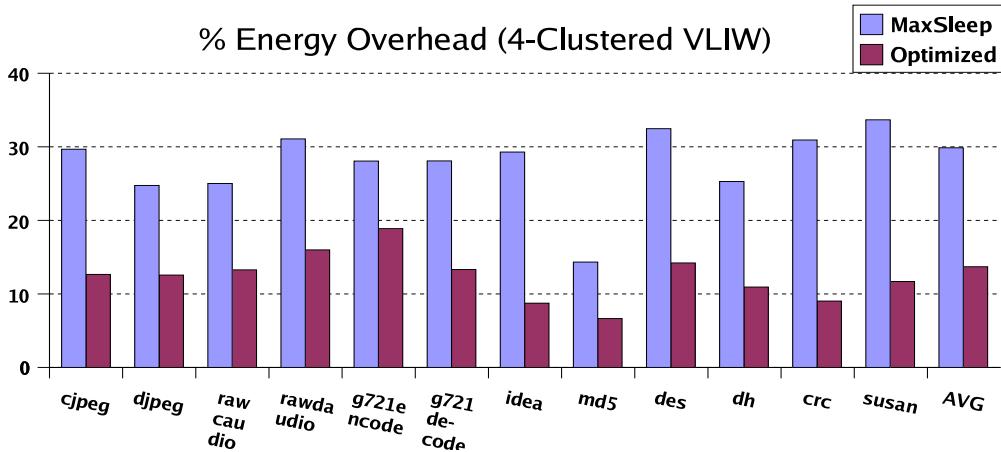

| 4.9  | % Increase in Functionl Unit Energy w.r.t Hypothetical No-overhead Scheme (4 Cluster) . . . . . | 62 |

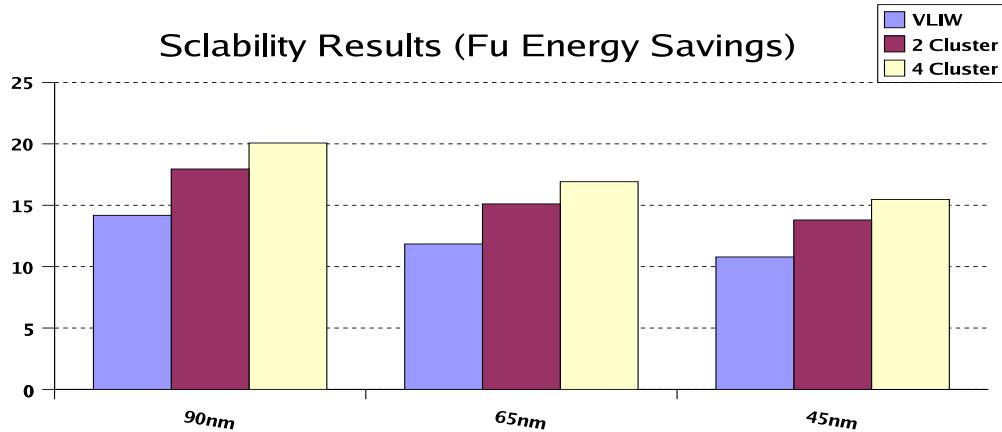

| 4.10 | Scalability Results for Functional Unit Energy Savings . . . . .                                | 63 |

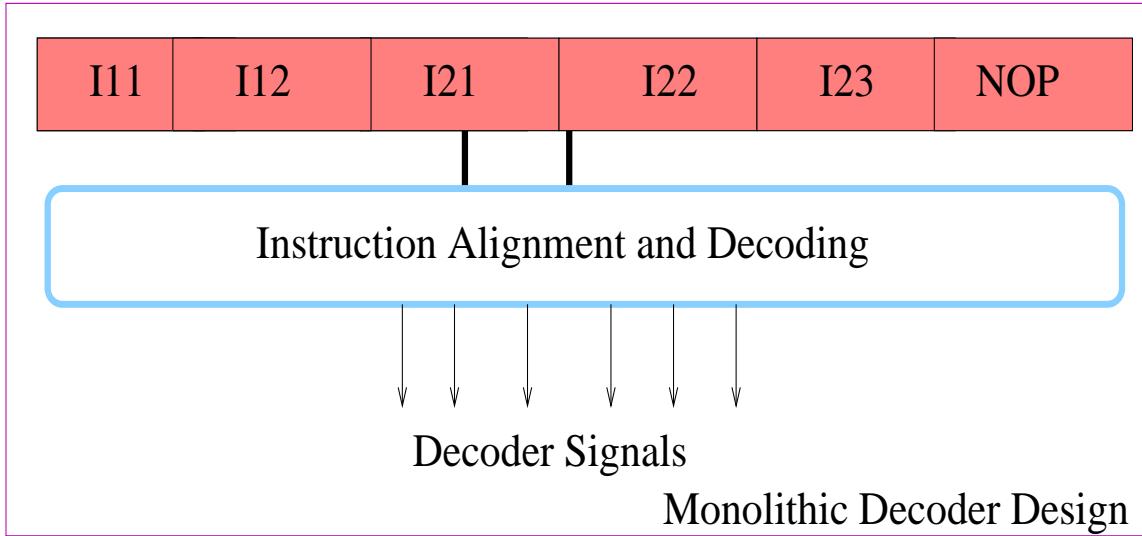

| 4.11 | Traditional Monolithic Decoder Design . . . . .                                                 | 64 |

| 4.12 | Split Decoder Design . . . . .                                                                  | 65 |

| 4.13 | % Reduction in Transitions with Scheduling w.r.t. Hardware only Scheme for ID                   | 66 |

---

|                                                                                                                                                               |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.14 % Increase in Energy w.r.t Hypothetical No-overhead Scheme for ID (VLIW) . . . . .                                                                       | 67  |

| 4.15 % Increase in Energy w.r.t No-overhead Scheme for ID (2 Cluster) . . . . .                                                                               | 67  |

| 4.16 % Increase in Energy w.r.t No-overhead Scheme for ID (4 Cluster) . . . . .                                                                               | 68  |

| <br>                                                                                                                                                          |     |

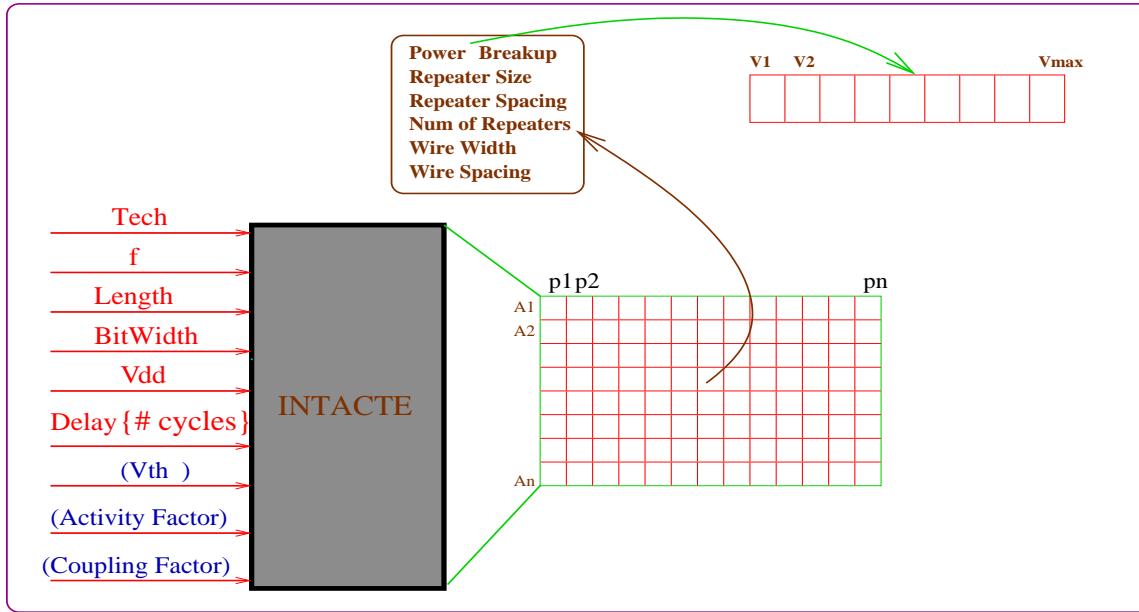

| 5.1 Overview of the INTACTE . . . . .                                                                                                                         | 78  |

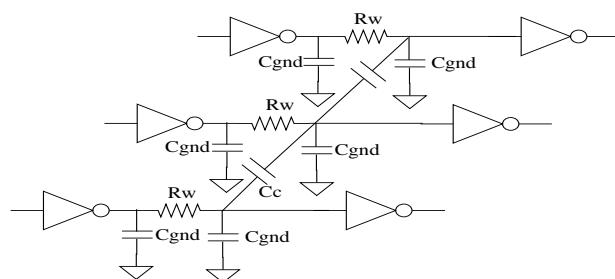

| 5.2 A Section of an On-chip Bus . . . . .                                                                                                                     | 81  |

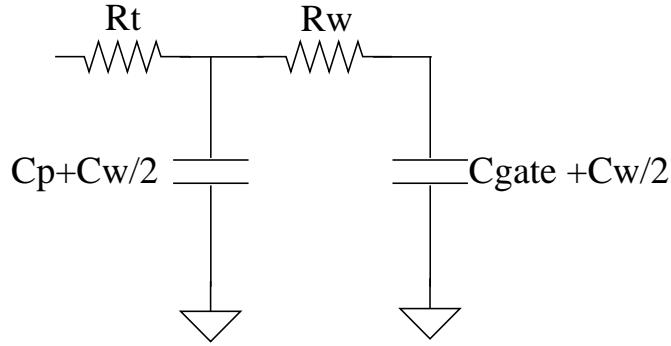

| 5.3 $\pi$ Model of the Interconnect . . . . .                                                                                                                 | 82  |

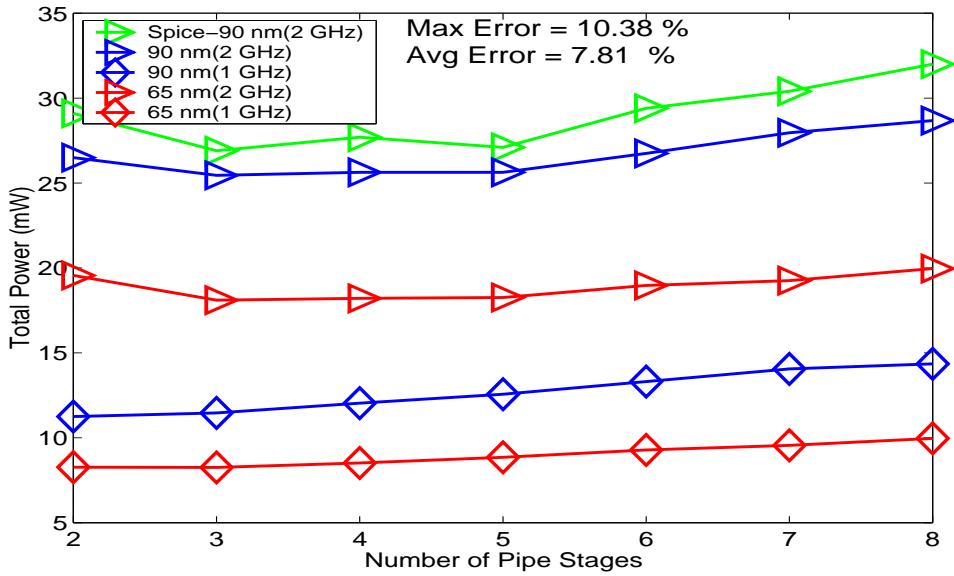

| 5.4 Degree of Pipelining vs Power for 5 mm Interconnect with $12 * \lambda$ Pitch . . . . .                                                                   | 86  |

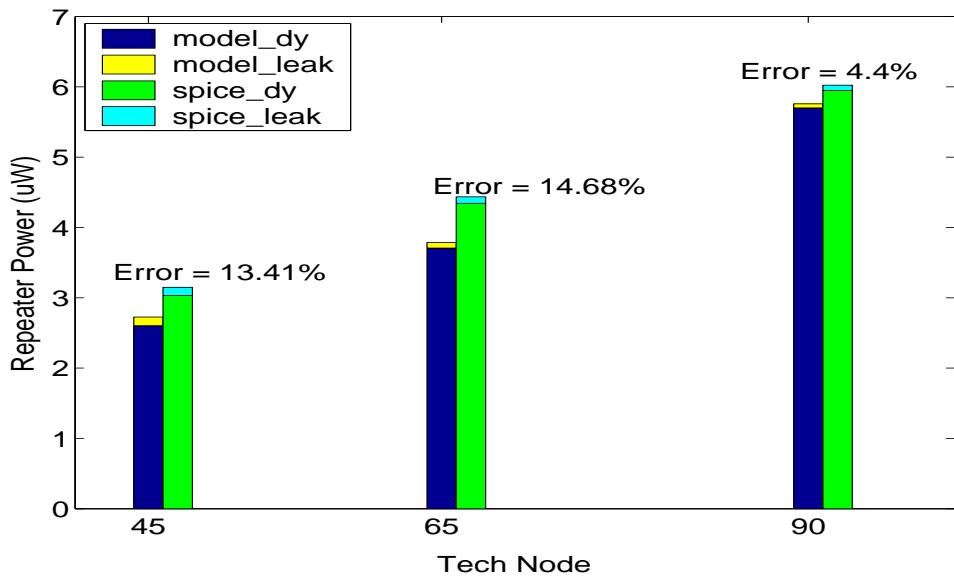

| 5.5 Validation of Dynamic and Leakage power for $1 \mu m$ Repeater Operated at 1GHz for Different Technology Nodes . . . . .                                  | 86  |

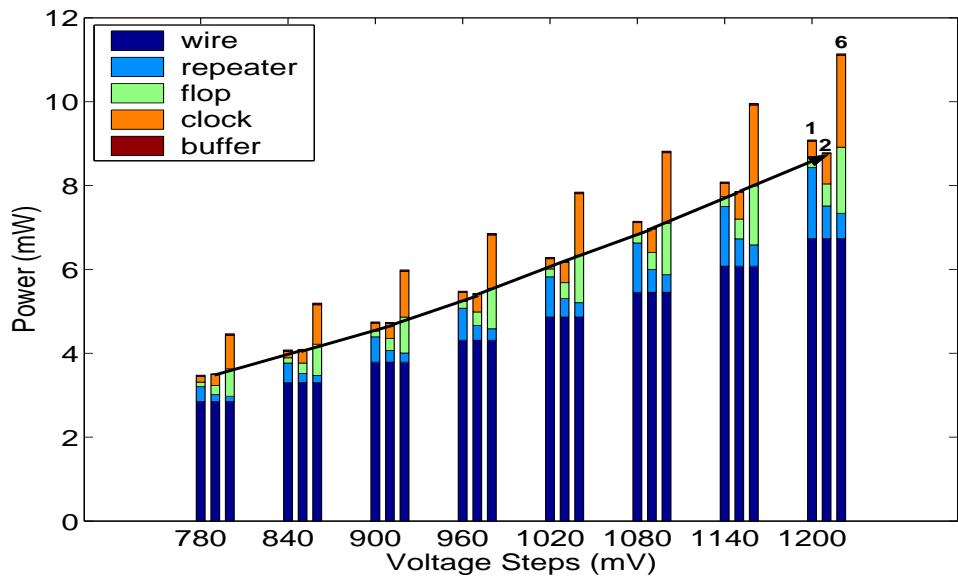

| 5.6 Component Wise Power Breakup for a 5 mm Interconnect with $16 * \lambda$ Pitch in 90 nm Tech Node Running at 1 GHz. . . . .                               | 87  |

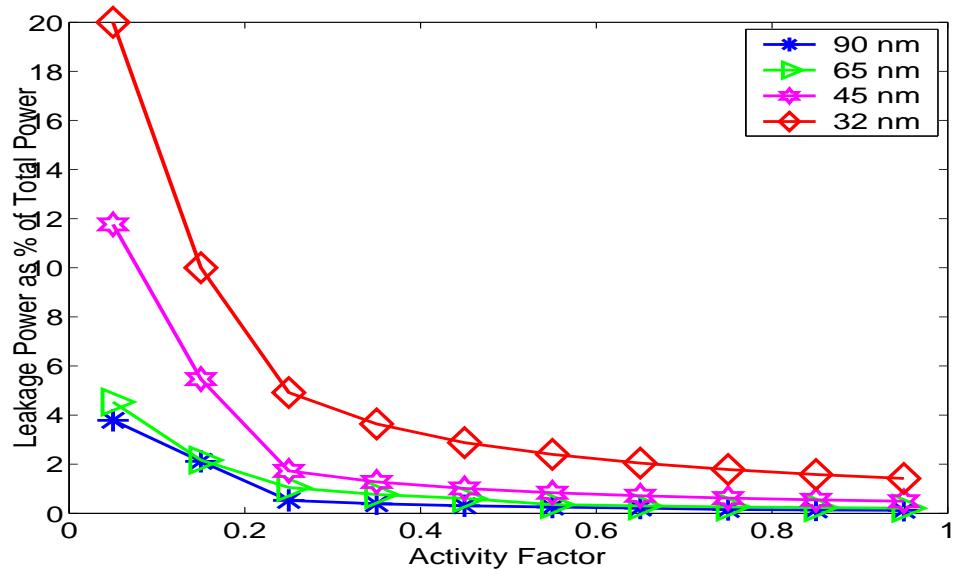

| 5.7 Leakage as % of Total Power for Different Activity Factors for Optimally Pipelined 5 mm Interconnect with $12 * \lambda$ Pitch Running at 1 GHz . . . . . | 87  |

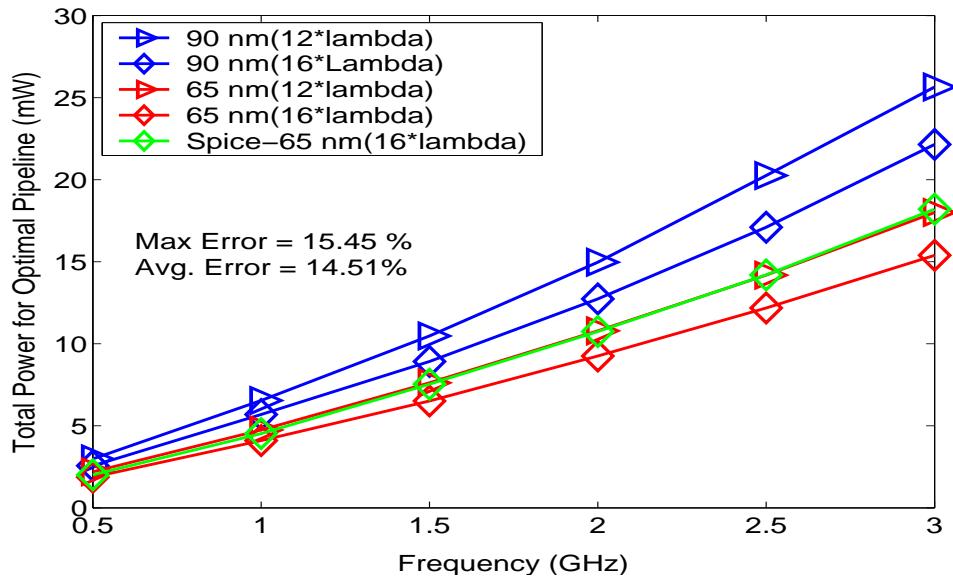

| 5.8 Frequency vs. Power for Optimal Degree of Pipelining for 4 mm Interconnect . .                                                                            | 88  |

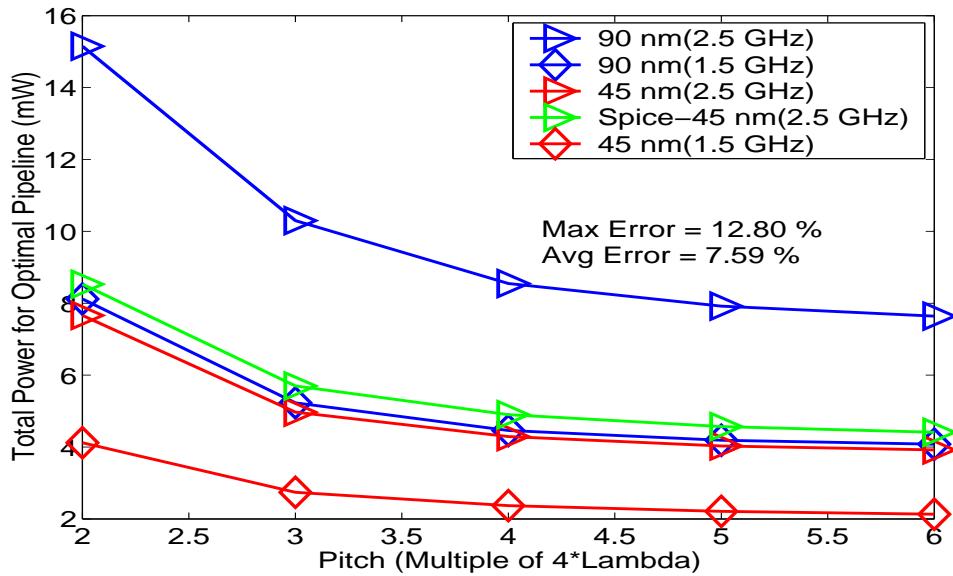

| 5.9 Pitch Vs Power for Optimal Degree of Pipelining for 2 mm Interconnect . . . . .                                                                           | 88  |

| <br>                                                                                                                                                          |     |

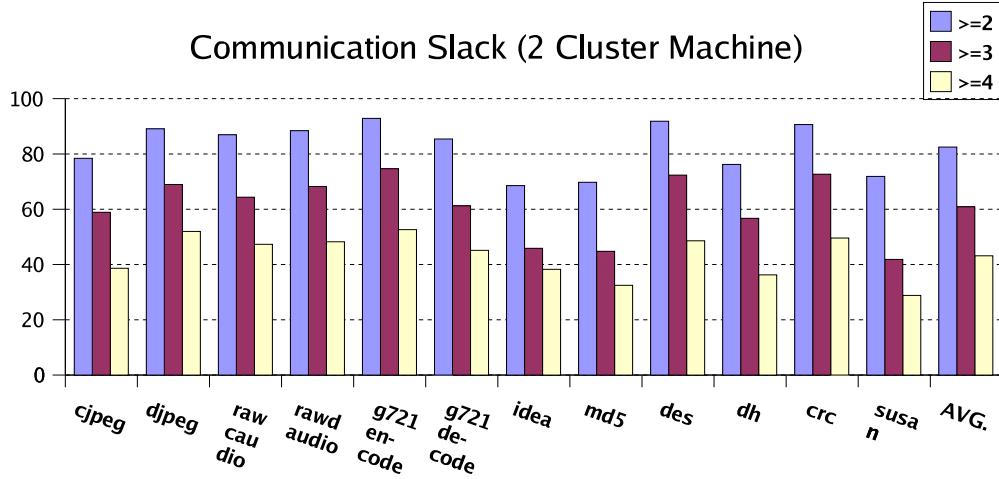

| 6.1 Communication Slack for Two-Cluster Machine Model . . . . .                                                                                               | 95  |

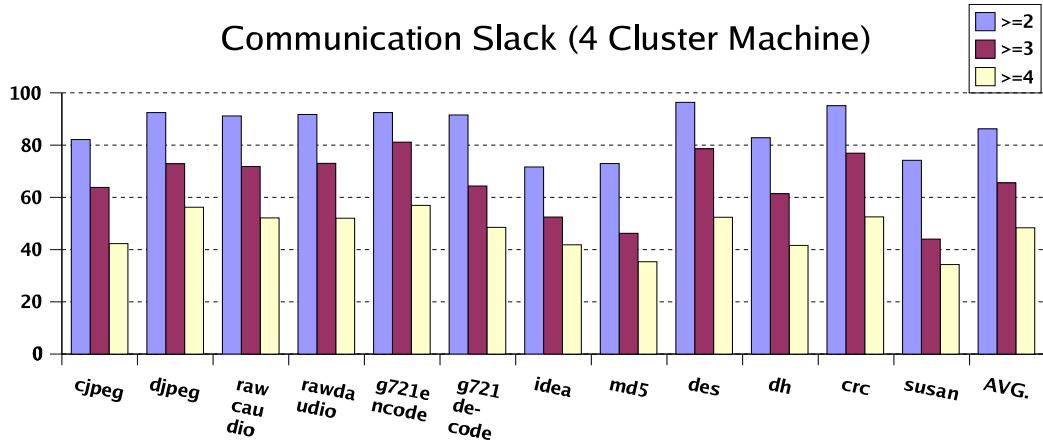

| 6.2 Communication Slack for Four-Cluster Machine Model . . . . .                                                                                              | 96  |

| 6.3 An Example Data Dependency Graph . . . . .                                                                                                                | 101 |

| 6.4 Possible Schedules For Clustered VLIW Architecture (a) Schedule 1 (b) Schedule 2                                                                          | 101 |

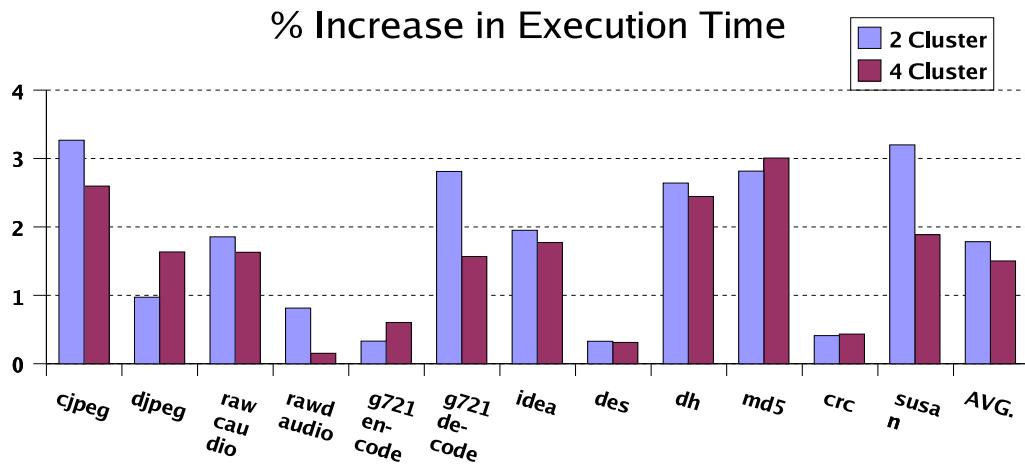

| 6.5 % Increase in Execution Time of LP Conf. w.r.t. LL Conf. . . . .                                                                                          | 104 |

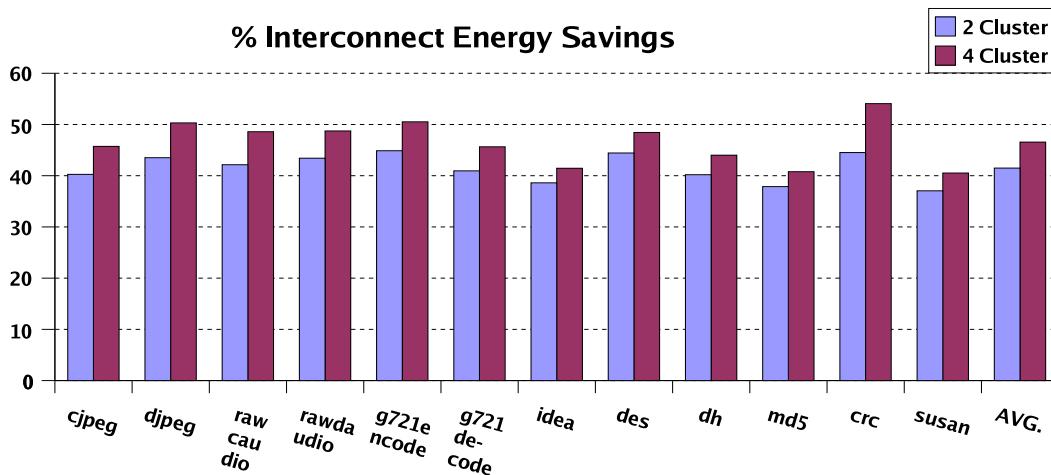

| 6.6 % Energy Benefit of LP Conf. w.r.t. LL Conf. . . . .                                                                                                      | 104 |

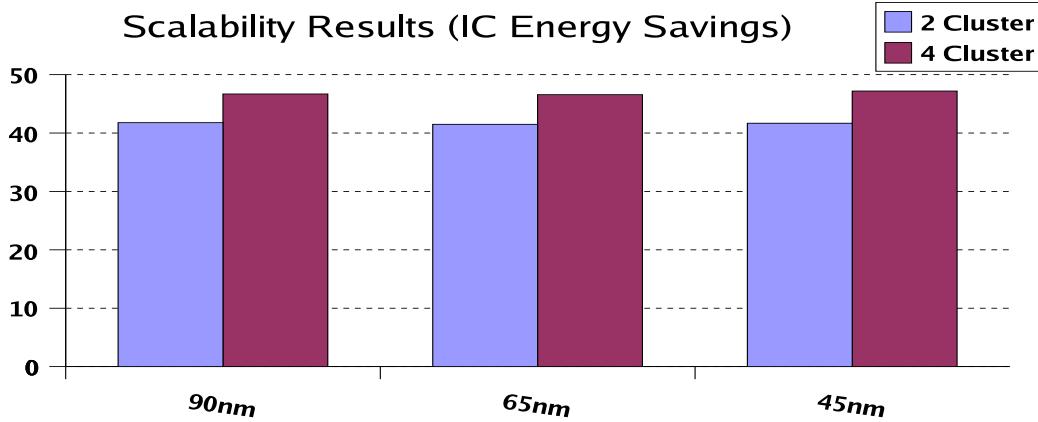

| 6.7 Scalability Results for Interconnect Energy Savings . . . . .                                                                                             | 105 |

| <br>                                                                                                                                                          |     |

| 7.1 % Increase in Execution Time of LP conf. w.r.t. LL conf. for Algorithm 5 . . . . .                                                                        | 117 |

| 7.2 % Energy Benefit of LP conf. w.r.t. LL conf. for Algorithm 5 . . . . .                                                                                    | 118 |

| 7.3 % Functional Unit Energy Benefits of Scheduling over H/W only scheme for Algorithm 5 . . . . .                                                            | 118 |

| 7.4 % Overall Benefit in EDP of Scheduling Algorithm 5 on LP conf. as compared to LL conf. and H/W only scheme for Fu Transitions . . . . .                   | 119 |

# List of Tables

|     |                                                       |    |

|-----|-------------------------------------------------------|----|

| 2.1 | Parameters in Power Equations 2.1, 2.2, 2.3 . . . . . | 12 |

| 3.1 | Description of Benchmark Programs . . . . .           | 42 |

| 3.2 | Latencies of Operations . . . . .                     | 42 |

| 3.3 | Clustered VLIW Configurations . . . . .               | 42 |

| 4.1 | Parameters of Energy Model in Equations 4.2 . . . . . | 58 |

| 5.1 | Symbols for Various Interconnect Components . . . . . | 83 |

# Chapter 1

## Introduction

Embedded systems have proliferated in our daily lives in the form of wearable computers, telecommunication appliances, consumer electronic devices, system controllers, and entertainment objects among many others. An embedded system can be loosely defined as a "*System employing a collection of hardware and software to perform a closely knitted set of functions and often working in a reactive and a time-constrained environment as a part of a larger system*". These systems are often employed to run multiple sophisticated algorithms demanding widely varying operation rates in hard or soft real-time mode. For example in a cellular phone, the speed of decoding must match that of normal conversation to ascertain a proper communication. Likewise, the controller of an atomic reactor should monitor several fluctuating parameters and exercise various controlling actions in a spur of the moment to avoid disastrous situations. If deadlines are violated, the quality of service may degrade to an unacceptable level or may even lead to catastrophic results in the case of a hard real-time system. Small size and less power consumption are critical factors in the design of hand-held battery-operated embedded systems. In general, less power consumption is desirable in all kinds of embedded systems because it reduces the operating cost of a device. Small form-factor necessary for many handheld embedded devices coupled with the requirement for powerful computing capabilities makes the temperature and associated reliability problems (specially for safety critical applications) another important consideration in the design of embedded systems. Thus embedded systems can be characterized by very high performance demand (to operate in real-time), low power consumption, low temperature, low cost, small form-factor, and high reliability.

The increasing ubiquity of embedded systems has opened up many new research issues as the design challenges posed by these systems are ostensibly different from those offered by general purpose systems due to their specific and conflicting requirements. New architectures leveraging the improvement in semiconductor technology have been developed. These exploit the abundant fine-grained instruction-level-parallelism (ILP)[1] available in embedded applications to satisfy their high performance requirements. Superscalar architectures[2] and very long instruction word (VLIW)[3] architectures are two traditional ILP design philosophies[1]. Both superscalar and VLIW processors have multiple pipelined functional units, which are connected to a single unified register file in parallel to attain better performance. A superscalar processor[2] uses dedicated hardware for scheduling instructions at run time. However, it suffers from the problems such as complicated design, large chip-area, and high power consumption attributed to the complicated runtime scheduling logic[4].

A VLIW architecture[3] gets rid of scheduling hardware and associated problems by exposing instruction latencies and delegating the task of scheduling to a compiler. High operation rates as required by emerging real time embedded applications can be attained by increasing the number of parallel functional units in a VLIW architecture. However, as the number of arithmetic units in a processor increases to higher levels, register storage and communication between arithmetic units become critical factors dominating the area, cycle time, and power dissipation of the processor. The cycle time is determined by the sum of wire delay and gate delay along the critical execution paths of a processor pipeline. Wire delays have become significant for the 0.25 micron CMOS process generation and centralized monolithic architectures (both superscalar and VLIW) which use long wires for connecting spatially separated resources may not benefit from the advancements in semiconductor technology[5][6]. The ever increasing trend towards miniaturization of devices makes utilizing huge transistor budget in a manner that enables high clock speed, low design complexity, and less energy consumption even more challenging[5]. However, resolving this challenge can enable the deployment of embedded systems for many performance-demanding never-before embedded applications at a lower cost. Another challenge posed by this technological advancement is the rising level of the leakage energy consumption in the logic. The increase in the transistor density requires reducing the supply voltage in order to operate the circuit reliably. The reduction in supply voltage also requires reduction in the threshold voltage in order to maintain the speedup and this leads to an exponential rise in

the leakage component of the energy consumption[7]. With the 65nm and smaller technologies currently in fabrication, the leakage energy is on par with the dynamic energy consumption. In future technologies the leakage energy will further dominate the overall energy consumption[8].

Clustered VLIW architectures(CVA)[9][10][11] have been proposed to overcome the difficulties with centralized architectures and to make them suitable for use in embedded systems. A clustered VLIW architecture[11] has more than one register file and connects only a subset of functional units to a register file. Groups of small computation clusters can be interconnected using some interconnection topology and communication can be enabled using any of the various inter-cluster communication models[12]. Clustering avoids area and power consumption problems of centralized register file architectures while retaining high clock speed which can be leveraged to get better performance. Texas Instrument's VelociTI[13], HP/ST's Lx[14], Analog's TigerSHARC[15], and BOPS' ManArray[16] are examples of the recent commercial micro-architectures developed based on clustered ILP philosophy. IBM's eLite[17] is a research proposal for a novel clustered architecture. Apart from clustered VLIW architectures, many other architectural philosophies[18][19][20][21][22] have also used distribution in its varied form to tackle the scalability problem in the past. This trend is expected to continue in the future also with ever growing number of transistors on the chip

Though clustering helps to combat the scalability problem by making components simpler and thereby increasing clock rate and reducing dynamic energy consumption of functional components, an interconnection network is required for the communication among different components. This communication happens over long wires having high load capacitance which in effect takes more time and incurs more energy consumption[5][23]. This problem is becoming severe with each upcoming process technology. As a result, clustered architectures are becoming more communication bound in terms of the performance and energy consumption. Apart from the interconnects, functional units are another major source of energy consumption in clustered architectures. The frequent accesses to functional units raises the temperature level and increases the leakage energy consumption which is specifically a concern in smaller technologies. Moreover, the contention for limited number of slow interconnects leads to many short idle cycles and that further increases the leakage energy consumption in functional units.

Clustered VLIW architectures rely on compile-time scheduling. The static scheduling simplifies the issue logic by alleviating the need for a dedicated hardware for scheduling. Thus, a

significant fraction of the total energy consumption in clustered VLIW architectures is attributed to interconnects and functional units. Though, the exact percentage depends upon the architecture and circuit details, earlier studies report that a very high percentage (20% to 30%) of total processor energy consumption is attributed to interconnects[24]. Similarly, a large fraction (30% to 35%) of static energy consumption in a VLIW architecture is attributed to functional units[25]. An architecture level model developed in [26] also confirms that the leakage energy consumption in functional units constitutes a noticeable fraction of the overall processor leakage energy consumption despite having a smaller transistor count compared to the caches. Thus, optimizing energy in interconnects and functional units in clustered architectures is becoming more and more important from one process generation to another.

However, the functional units and interconnects are often underutilized in clustered VLIW architectures. Apart from other usual causes such as data dependencies, the under-utilization of functional units is also due to the contention for limited number of slow interconnect channels that introduces many short idle cycles for functional units. At the same time since the functional units are distributed among clusters, there is also more contention for functional resources which leads to the underutilization of interconnects. Finally, the contention for functional and interconnect resources in clustered VLIW architecture combine in a synergistic fashion and lead to greater available slack in clustered architectures as compared to VLIW architectures.

The advancements in VLSI technology now enable designing interconnects and functional units with different power and performance modes. For example [27][28] show that using 45nm technology, it is possible to design wires consuming 1/5 the energy but having twice the delay[27]. [29] proposes to use interconnect composed of wires with different characteristics to improve the  $ED^2$  of the superscalar processor. Similarly, the capabilities of dual-threshold domino logic[30] with sleep mode (that can transition between active mode and sleep mode and vice versa without any performance penalty but with moderate energy penalty) can be utilized to do leakage energy management for short idle cycles in functional units. In this thesis, we propose a compiler-assisted approach that exploits the greater available slack and leverages on these advancements in VLSI technology to improve the usability of clustered VLIW architecture in smaller technologies, targeting the two major source of energy consumption namely interconnects and functional units.

## 1.1 The State-of-art

In the past, study of leakage energy management at the architectural level has mostly focused on storage structure such as cache[31][32][33]. Relatively, a little work has been done on architecture level leakage energy management in the context of functional units[34][35] of superscalar processors. Albonesi et al.,[34] propose a purely hardware based scheme in the context of a superscalar architecture for aggressive leakage energy management which is specifically useful for smaller technologies. However, being a purely hardware based scheme, it suffers from the problem of limited program view and thus the benefits are severely (on average, by 30%) affected by frequent transitions from active mode to sleep mode and vice-versa because of many short idle periods. Our compiler-directed approach for leakage energy management in functional units in the context of clustered VLIW processors leverage on global view of the schedule and greater available slack in the context of clustered VLIW architectures to directly improves over [34]. Though there has been some work in the direction of energy efficient scheduling in the context of VLIW architectures[36][25][37], to the best of our knowledge, there has been no such work for aggressive leakage energy management in the context of clustered VLIW architectures specifically targeting smaller technologies.

As compared to reducing energy consumption in function blocks, study of energy efficiency in interconnects is still in its infancy. Before proposing any architectural or compiler optimization for saving interconnect energy, one needs a model for high level estimation of interconnect delay and energy. However, prior research in interconnect modeling and analysis has mostly dealt with specific circuit level issues [28][38][39] and is not directly usable to make high level micro-architectural trade-offs. For example, an architect would be interested in knowing what are the available trade-offs in terms of pipeline latency and power, for a given bandwidth and interconnect distance. This information could be used at a higher level of design to obtain the overall optimum for the system. Hence, there is a need for a model or a tool for the interconnect, which can give reasonably accurate design points and their associated area and power costs for various architecture level constraints like bandwidth, latency etc. Similar models are available for caches[40], register files[41], and functional components[34]. Availability of an interconnect model will be very helpful for architects to involve interconnect in early design trade-offs. We fill this gap by proposing a high level interconnect energy and delay estimation model to get a fast but reasonably accurate estimates of interconnect delay, area, and power for a given technology,

wire length, bit-width, clock frequency and latency. In contrast to earlier circuit level models, the proposed model is directly useful for the architects and compiler designer to perform energy optimization in interconnects.

In the absence of any high level model for interconnect energy estimation, primary focus of research in past had been to reduce the latency of communication[42] and evaluation of various inter-cluster communication models[12]. We introduce the idea of heterogeneity in interconnects of clustered VLIW architecture. We also propose a notion of communication slack of data values and a scheduling scheme that exploits the communication slack to save significant energy in heterogeneous interconnect in the context of clustered VLIW architectures. Again to the best of our knowledge, we are not aware of any work targeting reduction of energy consumption in interconnects in clustered VLIW architectures.

The novelty of our approach also lies in an integrated scheduling algorithm that simultaneously reduces the energy consumption in functional units as well as interconnects. The contention for a limited number of functional and communication resources in a clustered VLIW architecture leads to increased cycles of execution on a clustered machine as compared to an equivalent VLIW machine. Our combined scheme aggregates the scheduling slack of instructions and communication slack of data values in a synergistic fashion to convert the inherent idleness of functional and communication resources in clustered architectures to energy gains.

## 1.2 Our Approach

VLIW and clustered VLIW architectures are optimized for peak performance in order to meet real-time performance requirements of embedded applications. However, functional units are underutilized due to the inherent variations in the ILP of programs. The idleness is even more pronounced for clustered VLIW architectures because of the contention for a limited number of slow interconnects which manifests itself in the form of many short idle cycles. We observe that functional units are idle for more than 70% cycles on an average in our collection of media benchmarks for a 2-clustered machine with moderate number of functional units. This idleness is not only because of data and resource dependencies but also because not all scheduling regions of the programs have the same amount of ILP. We also observe that roughly 50% of total 70% idle cycles have durations less than or equal to 10 cycles.

One way to reduce the number of idle cycles (attributed to contentions for cross-paths) and thereby improve performance is to use a high-speed high-bandwidth cross-path for communication of data values among clusters. Previous studies have reported that performance degrades by 12% when the latency of communication is doubled for a four clustered architecture, and that increasing the interconnection bandwidth from one to two improves the performance by as much as 10%[43]. We also observe a similar benefit in performance by using two bidirectional single-cycle cross-paths between clusters as compared to the configuration which uses only one cross-path. However, having both the cross-paths optimized for low latency results in high energy consumption in interconnects. This is because improving the latency of a communication channel requires closely spaced repeaters which increase the area and energy overheads of repeaters[27]. A high speed path for communication of data values among clusters indeed enables better performance, but we argue that not all data values are critical enough to be communicated on a high speed path, that many communications are non-critical and can still happen on a slow path without affecting performance. We introduce the notion of communication slack in the context of data values that captures the criticality of communication and we observe that on an average, 60% of communications can sustain a latency of three cycles or higher.

Thus a more suitable option to reduce the idleness in functional units without incurring a high energy overhead is to use heterogeneous interconnects between clusters with some paths optimized for latency and others for energy. We propose a scheduling mechanism that exploits the communication slack to steer the non-critical communication over the slower but energy-efficient wires while assigning critical communication over the fast but more energy-consuming wires. Such a configuration which uses one bidirectional single-cycle cross-paths and one bi-direction three-cycle cross-path between clusters reduces the number of idle cycles by 13% on an average as compared to the configuration which uses only one cross-path.

Though a high bandwidth cross-path mitigates the contentions for cross-path and improves performance to some extent, the variation in ILP of programs coupled with cross-path contention still manifest itself in the form of many short idle periods. Short idle periods render traditional leakage energy management schemes unusable. A hardware based scheme proposed by Albonesi et al.[34] utilizes the dual-threshold logic (and its capability of fast transition to and from low-leakage mode at moderate energy penalty) to perform leakage energy management for short

idle cycles. However, effective energy savings of this scheme is low because of the high energy cost and frequent transitions. We propose a scheme that exploits instruction slack to aggregate idleness in functional units and improves effective leakage energy savings by reducing frequent transitions. We also evaluate the energy benefit of our compiler-directed technique in the context of instruction decoder.

Finally, we propose a combined scheme that exploits the communication slack of data values as well as instruction slack to reduce the energy consumption in functional units and interconnects. The proposed scheme tries to keep idle functional unit idle while maximizing the utilization of active functional units. Similarly, the proposed scheme also exploits the communication slack of data values to utilize the low-power cross-path as much as possible. The major contributions of this thesis can be stated as follows:

1. We propose a compiler-directed leakage energy optimization technique in the context of VLIW/clustered VLIW architectures, targeting the underutilized components such as functional units and instruction decoder and evaluate its benefits. Significant benefits are obtained over and above that offered by a hardware based technique (which already obtains good leakage energy benefits) with negligible performance loss. Apart from obtaining energy benefits without performance loss, the proposed technique also reduces peak power and step power consumption that impact the reliability of the chip[44][45]. The proposed technique is particularly useful for smaller technologies demanding aggressive leakage energy management.

2. We also propose a high level model for interconnect energy and delay estimation that can be used by architects, micro-architects, and compiler designers to explore the interconnect design space and evaluate interconnect energy optimization. The proposed model fills the gap between architect's need and circuit level models. The model takes architectural parameters such as length, bit-width, latency, and target technology and provides a set of interconnect options with varying degree of area, pipelining, and power budget using pre-characterized estimates of circuit parameters for different interconnect components[46].

3. We introduce the notion of heterogeneity in interconnects and propose a compiler-directed technique for energy optimization in interconnects of clustered VLIW architectures. We evaluate the energy benefits of the proposed techniques using the proposed interconnect

energy model[47][46].

4. We propose integrated schemes for energy optimization in functional components as well as interconnects simultaneously in a novel fashion and evaluate the energy benefits of the combined schemes[48].

5. We also present a detailed performance evaluation of all the schemes by adapting Trimaran compiler infrastructure for clustered architectures.

### 1.3 Outline of the Thesis

Chapter 2 provides a brief survey of earlier work in the context of energy modeling, energy efficient architectures, energy optimization in hardware, software (both at OS level and at compiler level) as well as HW/SW co-optimization techniques. Chapter 3 describes the clustered VLIW architectures and our experimental framework. Chapter 4 describes a compiler-directed scheme for leakage energy optimization in functional units and instruction decoder of clustered VLIW architectures. We also provide an example that shows the energy benefits of the proposed scheme and a detailed performance evaluation for VLIW and clustered VLIW architectures showing the energy benefits of the proposed scheme. Chapter 5 presents a model that we have developed for interconnect delay and energy estimation. We also present results that show various interconnect design trends in different technologies and a detailed validation of the model based on circuit-level spice estimations. Chapter 6 describes compiler-directed interconnect energy optimization techniques in the context of clustered VLIW architectures. An example is presented to show the functioning of the scheme. A detailed performance evaluation is presented to show the benefit of the proposed scheme. Chapter 7 describes integrated techniques for energy optimization in both functional units and interconnects. Experimental results show the energy benefits of proposed scheme. Chapter 8 presents conclusions and future directions of this work.

# Chapter 2

## Related Work

This chapter presents a brief survey on earlier work in energy optimization. Section 1 provides basic power equations for CMOS circuits and demystifies various power-performance metrics in widespread use. Section 2 describes earlier work on circuit/logic level techniques for power optimization. Section 3 describes energy-efficient architectural design techniques. Section 4 deals with energy-efficient optimization at the software level i.e., at the operating system level, compiler level as well as application level. Section 5 describes some hardware/software co-optimization techniques for energy optimization. Section 6 briefly discusses some recent developments and advanced techniques for energy optimization found in commercial systems. Section 7 presents different approaches to energy modeling. Section 8 concludes this chapter with a mention of the limitations of the existing work.

### 2.1 Power Basics and Metrics

The power consumption in a CMOS circuit can be reasonably approximated by the three component Equations 2.1, 2.2, 2.3[7]. The parameters used in these equations are described in Table 2.1. The first equation represents dynamic or switching power. Switching power is the power consumed due to some work being performed i.e., activity happening in the circuit. In other words, it is the power consumed when the outputs of the gate switch, which electrically means charging and discharging of the output capacitance of the gate.

Activity factor represents the fraction of the gates that undergo switching because not all gates switch in every cycle. Dynamic power is the dominant component of power up to 90 nm

technology with the leakage being roughly 10% of the total power.

$$P = ACV^2 f + VI_{leak} + \tau AVI_{short}f \quad (2.1)$$

$$f_{max} \propto (V - V_{threshold})^2 / V \quad (2.2)$$

$$I_{leak} \propto \exp(-qV_{threshold}/(kT)) \quad (2.3)$$

However, with 65 nm and smaller technologies, leakage power represented by the second term of the equation becomes more dominant. Leakage power is consumed irrespective of whether activity happens in the circuit or not, i.e., it is present irrespective of any work being performed or otherwise. The major reason why leakage dominates in smaller technologies is as follows. The increase of transistor density from one technology to another requires reducing operating voltage in order to maintain the reliability of circuit operation. Though reducing voltage helps to reduce dynamic power quadratically, it also impacts the maximum operating frequency which, as Equation 2.2 shows has roughly linear dependence on operating voltage. Thus, in order to maintain speedup in the event of reducing voltage, threshold voltage should also be reduced. However, reduction in threshold voltage leads to exponential rise in leakage current as given by Equation 2.3. In 65 nm technology, leakage power is on par with dynamic power and it further increases in smaller technologies and this presents a significant power challenge.

The third component of power is attributed to short-circuit current that flows momentarily between ground and power supply during switching of the gate. Unlike leakage current, this component of power neither dominates nor exponentially increases.

Apart from these three power components, two other factors related to power have significant impact on design and reliability of circuits. Peak power is the maximum limit on power above which a circuit undergoes catastrophic damage and thus, the circuit should be operated below peak power all the time. Step power is the sharp change in power requirement of a circuit from one time step to another. This is also called ground bounce or  $di/dt$  noise which has an effect on voltage levels and can lead to erroneous behavior. Thus, it is required to avoid sharp changes in the power requirements of circuit for reliable circuit operation[7].

Whereas power is the correct measure for wall powered devices such as usual desktop PC and servers, energy is the correct measure for devices powered by batteries (such as cell phone, laptop etc.) which store a fixed amount of charge. This is because the amount of energy consumed

Table 2.1: Parameters in Power Equations 2.1, 2.2, 2.3

|                 |                                                               |

|-----------------|---------------------------------------------------------------|

| A               | Activity factor                                               |

| C               | Total capacitive load at the output of the gate               |

| V               | Operating voltage                                             |

| $V_{threshold}$ | Threshold voltage                                             |

| f               | Operating frequency                                           |

| $I_{short}$     | Short circuit current                                         |

| $f_{max}$       | Maximum operating frequency dictated by V and $V_{threshold}$ |

| T               | Operating temperature                                         |

| k               | Boltzmann's constant                                          |

| q               | Electronic charge                                             |

| $\tau$          | Duration of flow of the short circuit current                 |

for performing a task decides the lifetime of the battery in these devices. The computational efficiency of two devices is often compared using the metric, MIPS/watts. The impact of energy optimization is compared using product of energy and execution time popularly known as energy-delay product. The energy-delay product gives a fair measure of comparison and is immune to tricks. Techniques for dynamic voltage and frequency scaling are often compared using  $energy - delay^2$  that gives more weightage to performance loss than to energy savings as compared to just energy-delay product.  $Energy - delay^2$  is more useful for applications where high performance degradation is not desirable for energy savings.

## 2.2 Circuit and Logic Level Techniques

Various circuit and logic level techniques are available to design circuits with reduced effective capacitance, thereby reducing dynamic power consumption. Circuit level techniques have also been developed to reduce leakage power as well as power of interconnects. This section presents available techniques for reducing power consumption at the circuit design level.

### 2.2.1 Dynamic Energy Optimization in Logic

Reducing transistor width reduces power. However, it introduces more delay and thus, the implementation of this technique is done effectively by changing the width of a transistor based on its distance from the critical path[49]. Switching of a transistor leads to the switching of adjacent transistors as well and increases the overall power consumption. Thus, transistors are

often grouped together such that those that switch often are placed near the output of the circuit. This restructuring is often applied at multiple levels. For example, gates are often restructured in a chain topology and this reduces switching as compared to tree topology[50][51]. Half frequency clock synchronizes at rising as well as falling edge. In general, automation tools known as EDA tools are used to come up with the best implementation of a circuit by exploring many possible implementations to meet the desired delay, area, and power goals[52]. Half frequency clocks enable significant power savings by cutting down the operating frequency to half. Similar benefits can also be achieved by using half swing clocks that swing only to half the voltage[53]. However, implementation of half frequency and half swing clocks poses significant design problems that also exacerbates the already troublesome clock skew problem[53]. Apart from logic gates, the flip-flop which is the basic storage element, is also a major source of power consumption, especially because of spurious activity. Self-gating flip-flops and conditional capture flip-flop check this spurious activity and hence reduces power consumption due to spurious input changes[54][55].

### 2.2.2 Leakage Energy Optimization in Logic

As described earlier, leakage energy is expected to rise exponentially with technology scaling. Various circuit level techniques which aim to reduce the leakage energy have been proposed. The straightforward way of reducing leakage by increasing threshold voltage impacts speedup[7]. One technique exploits the stacking effect that says that two or more transistors stacked on each other consume less overall leakage because stacking induces a slight reverse bias between the gate and source of the bottom transistor. Thus, stacking increases the effective threshold voltage of the bottom transistor and hence reduces the leakage current. Another technique proposes to use a high threshold sleep transistor to isolate the leaky circuit element from supply voltage and ground, and thereby reduces leakage drastically when the circuit is inactive. However, it involves careful sizing of the sleep transistor, as otherwise, the overhead of activating it will be high[56]. A Multiple threshold circuit uses high threshold transistors on the critical path and low threshold transistors on non-critical paths but this technique calls upon a careful and difficult design[57]. Adaptive body biasing technique dynamically adjusts the threshold voltage of a circuit by applying a voltage to the body of a transistor depending on whether the circuit is active or not[58]. Leakage equation 2.3 shows the exponential dependence of leakage

on temperature which is specifically a concern for smaller technologies. Higher leakage leads to higher total energy consumption energy which in turn leads to more heat dissipation and hence high temperature. High temperature in turn increases leakage energy which increases temperature again. This vicious cycle can lead to a thermal runaway which may eventually damage the chip. Thus, circuit designers are looking at new ways of cooling the chip to check the temperature and its impact on leakage, such as refrigerating the chip and circulating cryogenic fluids such as liquid nitrogen[59]. Apart from reducing the leakage, reducing temperature also improves the performance and reliability of the chip.

### 2.2.3 Interconnect Energy Optimization

An interconnect is a place of high electrical activity and hence causes heavy energy consumption. Many proposals target to reduce the energy consumption in interconnects by reducing spurious transitions or by using only a part of the bus. Bus inversion transfers the actual values or inverted values depending on which causes less number of transitions. Apart from transitions, cross-talk among nearby wires also adds significantly to interconnect energy consumption. Shielding wires are introduced to reduce coupling among the wires. Self-shielding codes encode the value in such a way as to reduce cross-talk among neighbor wires[60]. Low-swing buses transfer a value with lower voltage and amplify it back to reduce energy consumption. However, this comes at the cost of extra hardware[61]. Bus segmentation divides a bus into segments and instead of keeping the whole bus active keeps only the desired segment active[62]. A network-on-chip extends the segmented bus idea to the whole chip by composing an interconnection network by rows and columns, which in turn are divided into segments and demarcated by tri-state buffers. Different segments are selectively updated as data passes through them[63].

## 2.3 Architectural Techniques for Power Optimization

Earlier work on architectural techniques for power optimization as described below has mostly focused on energy consumption of caches and issue queues that contribute significantly to overall processor energy consumption. Techniques proposed earlier either reduce the energy consumption of an access or reduce the total number of accesses. Splitting memory into smaller sub-banks and splitting banks into sub-banks enables energy savings by keeping only parts of the memory

active[64]. Further a compiler can help in clustering data into banks, thereby providing more energy savings[65]. Filter caches provide significant energy savings by introducing another level of cache between processor and L1 cache to filter many accesses[66]. Another idea is buffering a block from the cache and if access is from that block this saves energy. Scratch pad memory is software controlled memory (filled ahead of time) that resides on the chip and can be accessed in a single cycle[67]. Low power trace cache designs try to reduce the number of instruction cache accesses. Instead of accessing both instruction cache and trace cache, branch confidence estimation can be used to access either from the trace cache or from the instruction cache[68].

An adaptive Cache changes the state of a cache at the granularity of a line, block, or set[69]. A decay based approach simply puts the cache lines that are not in use after some time interval into drowsy or sleep mode[70][32]. Another approach determines hot spots by deciding the branch outcome (sufficiently taken branch target is a hot spot) and activates the cache lines accommodating the hot spot[71]. Deadline elimination based schemes power down cache lines containing basic blocks that have reached their final use[72]. The adaptive instruction queue technique divides the instruction issue queue into several partitions and activates only the desired partition[73]. Certain schemes use program IPC and compare it with IPC in an earlier interval or threshold to adjust the issue queue size[74]. Yet another approach deactivates the youngest part of instruction queues based on its contribution to overall IPC[75].

### 2.3.1 Dynamic Voltage Scaling

DVFS changes the processor voltage and frequency with changing workload of a processor to gain energy benefits without loosing performance. However, this deceptively simple idea involves various complications. Predicting workload is complicated because of arbitrary preemption and presence of modern features like pipelining, out-of-order execution, caches etc. Earlier work has focused on worst case execution time determination based on static analysis and measurement based prediction as well as combination of both. Moreover, the pipeline model and the cache model have been integrated into the compiler/simulator for better estimation. Nondeterminism and anomalies in real-time systems add to the complication of effective dynamic voltage and frequency scaling. Finally, DVFS mostly targets dynamic energy and often impacts performance. The rising level of leakage energy in smaller technologies can overwhelm the benefits of aggressive DVFS. The I/O which is powered at high voltage can also nullify the

benefits of even a tremendous saving in energy in the microprocessor part because of longer execution[76].

These are the different approaches to DVS. An interval based approach determines the usage of CPU in previous interval(s) to determine the processor speed for the next interval. They differ in determination of future processor utilization[77]. These are good for regular intervals but not for irregular intervals. Inter-task approaches monitor the hardware using hardware performance counters while the process executes, and determines the different frequencies for different processes based on these to save energy[78]. Inter-task DVS however suffers from two drawbacks.

- The approach is unaware of program structure and don't utilize it to determine processor speed. Flaunter et al.,[33] try to address this problem.

- Task workloads are usually unknown and it works based on the assumption that perfect knowledge of workload is available. Some also use history based workload prediction.

These limitations cause problems for irregular workloads. In contrast, Intra-task approaches adjust the processor speed and voltage within a task. One approach divides each task into time-slots and sets the processor speed to the slowest needed to finish the execution up to this time slot based on earlier worst-case execution time of the whole task[79][80]. Compiler level intra-task algorithm due to Shin and Kim,[81] determines the execution time of different program paths by profiling and inserts instructions to adjust frequency at the start of a different path, based on how far away is a path from the critical path. Hsu and Kremer's[82], approach is to generate a table of execution time and energy consumption for different regions and for different frequency combination and choose the best frequency combination for each region.

MCD architectures stand in between the fully synchronous and fully asynchronous architectures and are often called as globally asynchronous locally synchronous architectures[83]. An MCD architecture divides a processor into multiple domains for which frequency and voltage can be individually chosen. Absence of global clock makes MCD architectures, specifically useful to deal with the problem of clock skew which is increasingly troublesome for smaller technologies. DVS can provide more benefit for MCD architectures. However, communication among different domains in MCD architectures make the DVS problem even more complicated in the context of MCD architectures. Runtime DVS algorithms for MCD use issue queue usage for each domain to

get a load estimate and accordingly determine the frequency for each domain. Whereas, earlier algorithms make their decision after a fixed interval[84], later improvisation adaptively decides when to apply DVS[85]. A profile based approach[86] executes the program to obtain a runtime dependence graph of the program. A Shaker algorithm[86] then works on the graph from the root to the leaves and from the leaves to the root, to determine the operations with excessive energy dissipation and stretch their execution to get energy benefits until no operation has slack or give energy benefits. The feedback from this algorithm is used to select clock frequencies for different regions[86].

### 2.3.2 Leakage Energy Management of Other Devices

As mentioned earlier, leakage energy is dominating the overall energy consumption in smaller technologies. Resource hibernation or putting the idle resources into low leakage mode is a popular technique to reduce the leakage energy consumption. This technique has been applied on various components and at various levels.

Displays are the largest consumer of power. The traditional way is to dim the display after a threshold amount of no-response time. Face-off technique photographs the display perception and powers down the display if the face is not recognized. The associated cost of photography is being addressed by less energy consuming heat sensors to control the photography[87]. Zoned back-lighting technique is based on the assumption that the user is interested in only a part of the display. This scheme keeps only the focused window bright and rest of windows are dimmed[88].

Disk drives are another large consumers of power and most of this is attributed to rotating platters. One technique puts a platter into hibernation after a threshold amount of time[89]. Low threshold means more savings but also the risk of more energy and performance loss because of bumps. High thresholds may miss potential savings. An adaptive scheme increases and decreases the threshold dynamically to adapt to the usage and provides more effective energy savings[89]. Another scheme that is more useful in servers (where idleness is not very frequent) is to charge the RPM based on input queue size and system response time[90]. Operating systems can further help by clustering disk usage requests[91].

## 2.4 Software Level Power management

### 2.4.1 Compiler-Directed Power Management

Traditionally, performance oriented compiler optimization are used to provide implicit energy benefits. [92] demonstrated that loop transformations provide energy benefits in memory but increase the CPU energy dissipation. [93] found that optimizations that reduce workload to improve performance such as common subexpression elimination, copy propagation and loop invariant code motion also reduce the CPU energy dissipation. However, correlation between performance optimization and optimization for low power is not true in general. Moreover, not all performance oriented optimizations improve peak power dissipation. For example, software pipelining and loop unrolling actually increase peak power dissipation because more ILP is exploited. Thus, many compiler techniques have been developed to reduce power and energy explicitly in different components. Compiler optimizations can reduce the number of memory accesses by keeping the data closer to the processor and reduce access energy consumption by judicious assignment of data to memory locations. [94] proposes various compiler techniques using state-preserving and state-destroying low-leakage cache modes that determine last usage of instruction and place the corresponding instruction cache lines into the appropriate state. [95] exploits data locality and proposes compiler techniques to keep only a part of the data cache (needed by current computation) active in order to save energy in data caches.

As compared to storage structures, compiler level techniques for reducing energy consumption in functional components and interconnects are rather scarce and are mostly proposed in the context of superscalar and flat VLIW architectures. Zhang et al., have proposed a rescheduling scheme to reduce dynamic and leakage energy in the functional units of a VLIW processor by exploiting the remnant slack of a performance-oriented schedule[61]. Kim et al.,[25] have proposed a leakage energy management scheme for VLIW processors that approximates the ILP available in the program using heuristics. The calculation is at the coarser loop level granularity assuming that there is little variation in the ILP within the loop. Their scheme keeps only canonical subset of functional units that is sufficient to exploit this approximated ILP in the active state. Gupta et al.,[35] propose a novel data structure called power-aware flow graph. Their leakage energy management scheme in the context of superscalar processors works over this graph to determine larger program regions called power blocks which offer opportunities to

save leakage energy. ISA and architectural support is needed to switch the functional unit on and off at the boundaries of power blocks and nullify spurious switching. Kim et al.,[37] have proposed a modulo scheduling algorithm that produces a more balanced schedule for software pipelined loops with an objective to reduce the peak power and step power. Lee et al.,[96] propose an optimal horizontal rescheduling and a heuristic vertical rescheduling algorithm that exploits the slacks in already scheduled code to minimize the transition activity on instruction buses (used to transfer instruction from instruction memory to decoder), thereby reducing the power consumption due to transition activity on the instruction bus. We compare and contrast our proposal with these earlier approaches in the area of compiler-directed energy management in the respective chapters.

Remote compilation and remote execution are other challenging areas for energy optimization. It has been observed that it is energy efficient to compile remotely if compilation time exceeds the execution time[97]. However, the best strategy would be to execute, even the code remotely and just transfer the result just in time[98].[98] also investigates various static and dynamic methods of partitioning the code for remote compilation and execution. While the static method decides at compile time which method would be executed remotely, dynamic methods are superior in the sense that they dynamically make these decisions based on each call-site[98].

#### 2.4.2 Application and OS Level Power Management

Application transformation and adaptation techniques abstract an application as a software architecture graph that consists of processes, event handlers, and inter-process communication mechanisms (IPCM). It considers the base energy consumption of applications and then repetitively applies transformations to applications such as margin processes and replaces costly IPCM with cheaper IPCM to attain an energy optimized version of the application[99]. Other popular techniques are: trading the accuracy of computation with energy consumption[100] and reducing energy consumption by trading off the fidelity[88]. Application usage is monitored and signal is given when the usage falls below the requested level. Application lowers the quality of service until resources are plentiful. Echos system abstracts the resources as monetary objects. The applications are distributed currency based on currently desired battery rate and the currency is consumed to use resources. The application is interrupted when the currency is depleted[101].

Application hints can be very useful in improving the energy efficiency of systems. Some

software architectures consider systems as composed of two APIs. An API that allows application to communicate with the OS and another API that allows the OS to communicate with the hardware. An application can specify its power performance trade-off by giving the usage, deadline etc., for resources and these trade-offs are used by the OS for managing resources[102]. For example, an application can check if the disk drive is in sleep mode and whether it is costly to access it, Then the data can be accessed through the network. Thus, an application has abstract control over devices which is mapped by the OS to exact control. Similarly, a compiler can cluster disk accesses and network accesses by applying transformations and then add hints for the OS for clustered accesses to the disk. The OS can use this hint to process a batch of disk accesses and put the disk into sleep mode after processing[103].

## 2.5 Hardware/Software Co-Optimization

A cross-layer scheme applies power management at different levels i.e., at hardware, operating system, compiler, and application levels. The four major advances in this area are as follows :

Forge system[104] is an integrated power management framework for networked multimedia systems (specifically targeting video frame requests) that uses DVS, leakage control mode, and other architectural adaptation such as cache ways and register file size at architecture level. It has control knobs at OS and compiler levels to control these adaptations and a distributed middle-ware (at mobile device and proxy server) that takes feedback from the mobile device about energy statistics and decides the network traffic regulation and quality of service. Different heuristics are used at different levels but the whole system works in coordination with feedback, for integrated energy management[104].

Grace[105] is a cross-layer adaptation framework targeting real-time multimedia workload and integrating dynamic voltage scaling, power-aware task scheduling, and QoS settings. Grace works with two layers: a global layer that makes decisions less frequently because of high cost and a local layer which is more active in decision making. The local layer controls CPU frequency, task scheduling and adapts QoS parameters within the task. The information about a task is also broadcast to other tasks. Major variations such as low- battery level and large workload variations trigger the global adapter[105].

Another four layer system proposed by Fei[106] has two system layers of Hardware and OS

and two user level layers of middle-ware and application. The application declares its energy requirement for a range of QoS levels before getting admitted into the system. This information coupled with the information about battery levels (determined by OS) is used by the middle-ware to determine the systems settings. These setting are communicated to the OS before admitting the application process in to the system[106].

Another work[107] proposes a mixed Compiler-OS approach targeting real-time systems with fixed deadlines and worst case execution time requirements where the compiler emits code to put remaining worst-case execution time values into register and OS reads these value to set system settings accordingly[107].

## 2.6 Power Management in Commercial Processor

The Pentium 4 processor though designed from the performance perspective also features a thermal detection and response mechanism that inhibits the processor's clock from reaching most parts of the processor if the temperature enters the danger zone. It also features a register using which the operating voltage and frequency can be set to either high mode (wall-powered/high performance) or low mode (battery powered/energy efficient)[108]. Pentium M processor is specifically designed for the handheld domain. Thus, the architecture has several features that balance performance and energy consumption. The major features targeting energy efficiency include hardware for predicting idle units and inhibiting the clock signal, activating only a part of the bus needed for requisite communication, and execution stacking that clusters together units that perform similar functions. It also supports six different voltage-frequency settings for DVFS and low leakage transistors in the cache for reducing leakage energy[109]. Intel PXA27x processors use a profiler to determine the memory bounded-ness of programs using hardware performance counters and use this to decide the power modes of the processor.